# An Enhanced Voltage Sag Compensation Scheme for Dynamic Voltage Restorer

Abdul Mannan Rauf and Vinod Khadkikar, Member, IEEE

Abstract—This paper deals with improving the voltage quality of sensitive loads from voltage sags using a dynamic voltage restorer (DVR). The higher active power requirement associated with voltage phase jump compensation has caused a substantial rise in size and cost of the dc link energy storage system of DVR. The existing control strategies either mitigate the phase jump or improve the utilization of dc link energy by the following: 1) reducing the amplitude of the injected voltage or 2) optimizing the dc bus energy support. In this paper, an enhanced sag compensation strategy is proposed, which mitigates the phase jump in the load voltage while improving the overall sag compensation time. An analytical study shows that the proposed method significantly increases the DVR sag support time (more than 50%) compared with the existing phase jump compensation methods. This enhancement can also be seen as a considerable reduction in dc link capacitor size for new installation. The performance of the proposed method is evaluated using simulation study and finally verified experimentally on a scaled laboratory prototype.

Index Terms—Dynamic voltage restorer (DVR), voltage phase jump compensation, voltage sag compensation, voltage source inverter (VSI).

#### I. INTRODUCTION

N industrial distribution systems, the grid voltage disturbances (voltage sags, swells, flicker, and harmonics) are the most common power quality problems [1]. Sag, being the most frequent voltage disturbance, is typically caused by a fault at the remote bus and is always accompanied by a phase angle jump. The phase jump in the voltage can initiate transient current in the capacitors, transformers, and motors [2]. It can also disturb the operation of commutated converters and may lead to glitch in the performance of thyristor-based loads [3]. It is therefore imperative to protect sensitive loads, especially from the voltage sags with phase jump [4].

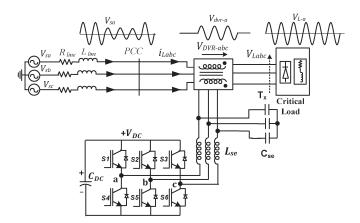

To protect sensitive loads from grid voltage sags, custom power devices (such as SVC, D-STATCOM, dynamic voltage restorer (DVR), and UPQC) are being widely used [5]–[8]. Among these devices, DVR has emerged as the most cost-effective and comprehensive solution [9]–[11]. The system configuration of a DVR is shown in Fig. 1. It consists of a dc link capacitor (serving as an energy reserve for DVR), a

Manuscript received May 8, 2014; revised July 14, 2014; accepted August 14, 2014. Date of publication October 8, 2014; date of current version April 8, 2015.

The authors are with the Institute Center for Energy, Masdar Institute of Science and Technology, Abu Dhabi, United Arab Emirates (e-mail: arauf@masdar.ac.ae; vkhadkikar@masdar.ac.ae).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2014.2362096

Fig. 1. Basic DVR-based system configuration.

series injection transformer, a six-switch voltage source inverter (VSI), and an LC filter for removing switching harmonics from the injected voltage. The primary function of the DVR is to inject a voltage with certain magnitude and phase in series with the upstream source voltage such that the load connected downstream always sees the pure sinusoidal voltage at its terminals.

Numerous control strategies for DVR have been reported in the literature [12]. The emphasis is on either reducing the voltage rating of DVR by aligning the injected voltage with the source voltage (i.e., in-phase compensation) or minimizing the dc storage capacity by using the reactive power compensation/energy-optimized approach [12]–[14]. All of these methods, however, cannot correct the phase jump and thus can result in premature tripping of sensitive loads [15].

The only possible way to mitigate the phase jump is to restore the load voltage to the prefault value. Such an approach is addressed as presag compensation in [13]. However, the phase jump compensation using the presag method requires a significant amount of active power from the dc link capacitor. Thus, this method will require a larger size capacitor or will result in shorter sag support time. In [16] and [17], an interesting technique is proposed to increase the compensation time while mitigating the voltage phase jump. In this method, once the dc link voltage drops to the threshold limit, the magnitude of the injected voltage is reduced by synchronizing the phase-locked loop (PLL) to the grid voltage. This allows further utilization of the dc link capacitor energy and extends the compensation time by some extent. However, it continues to consume the energy in the dc link capacitor throughout the duration of compensation and imposes limitation on compensation time enhancement.

This paper proposes a new control strategy in which the main objective is to enhance the sag compensation time while mitigating the voltage phase jump. The proposed method aims at

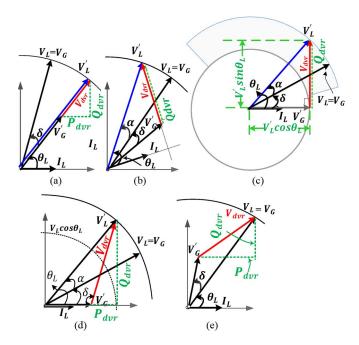

Fig. 2. Per-phase phasor representation of the basic compensation topologies for DVR. (a) In-phase injection. (b) Quadrature injection. (c) Quadrature injection limiting case. (d) Energy-optimized injection. (e) Presag injection.

regulating the contribution of active power to the least possible value. To avoid the problem of overmodulation, in the case of deeper sag depth, an iterative loop is employed in the control block. It is found that the proposed method can result in more than 50% additional sag support time when compared with the method in [16] and [17]. The performance of the proposed method is validated using simulation as well as experimental studies.

#### II. OVERVIEW OF DVR OPERATION

In this section, different sag compensation approaches [12]–[15] are briefly discussed. The phasor representations of these methods are given in Fig. 2. The phasors  $\vec{V}_G$  and  $\vec{V}_G'$  represent the rated and sagged grid voltages, respectively, whereas  $\vec{V}_L$  and  $\vec{V}_L'$  are the load voltages before and after the sag. To effectively highlight the differences among these methods,  $P_{\rm DVR}$  and  $Q_{\rm DVR}$  are also incorporated in the phasor diagrams. This is mainly to illustrate the amount of active and reactive powers demanded by each method. All of the quantities are drawn considering the load current  $(\vec{I}_L)$  as reference phasor.

#### A. In-Phase Compensation

In this type of compensation, DVR injects the smallest possible voltage magnitude in phase with the sagged grid voltage. However, as seen from Fig. 2(a), this method cannot correct the phase jump. The DVR-injected voltage magnitude and angle are given as

$$V_{\rm DVR} = \sqrt{2} \left( V_L - V_G' \right) \tag{1}$$

$$\angle V_{\text{DVR}} = \theta_L.$$

(2)

#### B. Quadrature Injection (Reactive Compensation)

In this method, the DVR injects voltage in quadrature with the load current, i.e., it corrects the sag with only reactive power. Using Fig. 2(b), the injected voltage magnitude and angle are given as

$$V_{\rm DVR} = \sqrt{2} \sqrt{V_L^2 + V_G'^2 - 2V_L V_G' \cos(\alpha + \delta)}$$

(3)

$$\angle V_{\rm DVR} = \frac{\pi}{2}$$

(4)

where  $\delta$  is the phase jump in the grid voltage due to the sag and  $\alpha$  is the phase jump induced due to reactive power compensation. As reported in [12], the maximum sag depth  $(\Delta V_{\rm sag,max})$  that can be compensated using quadrature injection is closely related with the load power factor and can be expressed as

$$\Delta V_{\text{sag-max}} \le (1 - \cos \theta_L). \tag{5}$$

The corresponding maximum injected voltage is given as

$$V_{\rm DVR-max} = \frac{V_G'}{1 - \Delta V_{\rm sag max}} \sin \theta_L. \tag{6}$$

Fig. 2(c) shows the limiting case for quadrature injection where DVR supports the full load reactive power while the grid operates at unity power factor.

#### C. Energy-Optimized Injection

This method is developed in [15] to enhance the performance of the quadrature injection method for the sag depth deeper than the limit in (5), where the DVR injects certain active power. The DVR voltage magnitude and injection angle can be calculated from Fig. 2(d)

$$V_{\rm DVR} = \sqrt{2} \sqrt{V_L^2 + V_G'^2 - 2V_L V_G' \cos(\theta_L)}$$

(7)

$$\angle V_{\rm DVR} = \tan^{-1} \left( \frac{V_L(\sin \theta_L)}{V_L \cos \theta_L - V_G'} \right). \tag{8}$$

#### D. Presag Compensation

In this method, both load voltage magnitude and phase are restored to presag values. Unlike the previous methods in Fig. 2(a), (b), and (d), the presag method in Fig. 2(e) can successfully compensate the phase jump. However, this phase jump correction requires an additional active power from the dc link capacitor.

A positive phase jump leads to an increase in angle between the grid voltage and the load current, increasing the active power burden on DVR compared to negative phase jump. Using Fig. 2(e), the injected voltage magnitude and angle can be written as

$$V_{\rm DVR} = \sqrt{2} \sqrt{V_L^2 + V_G'^2 - 2V_L V_G' \cos(\delta)}$$

(9)

$$\angle V_{\text{DVR}} = \tan^{-1} \left( \frac{V_L \sin \theta_L - V_G' \sin(\theta_L - \delta)}{V_L \cos \theta_L - V_G' \cos(\theta_L - \delta)} \right). \tag{10}$$

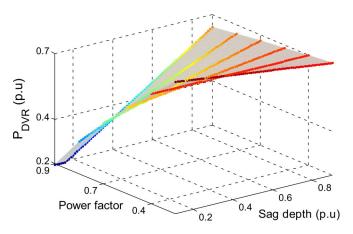

Fig. 3. Active power associated with the presag compensation method for different sag depths (phase jump  $=25^{\circ}$ ).

## III. POWER FLOW ANALYSIS AND MAXIMUM COMPENSATION TIME

As explained earlier, the presag method is the most energy-intensive method, and the injected power can be quite high even for shallow sag depths. Based on the phasor diagram of Fig. 2(e) [(9) and (10)], the active power associated with the presag method can be expressed in terms of sag depth, phase jump, and load power factor as given in the following:

$$P_{\text{presag}} = \sqrt{3}V_L I_L(\cos(\theta_L) - (1 - \Delta V_{\text{sag}})\cos(\theta_L - \delta). \tag{11}$$

A detailed derivation of (11) is given in Appendix A. Fig. 3 shows the DVR active power for a range of variation in sag depth  $(0.1 \le \Delta V_{\rm sag} \le 0.9)$  and power factor  $(0.4 \le \cos \theta_L \le 0.9)$ . The phase jump  $\delta$  is fixed at  $+25^{\circ}$ . As seen from the graph of Fig. 3, the active power supplied by DVR is relatively high (> 0.4 p.u.) for the presag method.

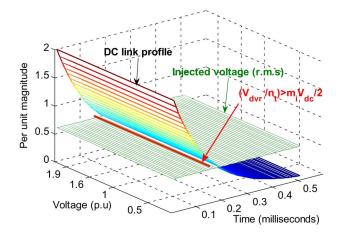

The theoretical power flow analysis conducted previously holds true as long as there is a significant amount of energy in the dc link capacitor. However, in the actual system, since it has a finite amount of energy, the voltage across the dc link capacitor  $V_{\rm dc}$  reduces. The following relationship should be satisfied at all time in order to achieve the adequate operation of DVR-VSI [18]:

$$\frac{V_{\rm dvr}}{n_t} \le \frac{m_{i-\max}V_{\rm dc}}{2} \tag{12}$$

where  $n_t$  is the turns ratio of the series transformer and  $m_{i-\max}$  is the maximum modulation index of VSI.  $V_{\rm dvr}$  is the injected phase to neutral voltage.  $V_{\rm dc}$  is the dc link voltage. As soon as the dc link voltage decreases below  $V_{\rm dc-min}$ , i.e., the limit set by (12), the DVR controller must stop the compensation process to avoid harmonics contamination in the load voltage.

The energy stored in the dc link capacitor is equal to

$$E_{c-dc} = \frac{1}{2} C_{dc} V_{dc}^2.$$

(13)

The power flow out of the dc link capacitor in the steady state is given as

$$P_{c-\mathrm{dc}} = \frac{1}{2} C_{\mathrm{dc}} \frac{d}{dt} V_{\mathrm{dc}}^2. \tag{14}$$

Fig. 4. DC link capacitor voltage profile during presag injection.

Considering a lossless DVR system, the dc power in (14) can be equated with the ac power of (11) to find the capacitor size. However, owing to the flow of active power, the dc link voltage drops, and the limit in (12) can be violated. This limitation restrains the DVR operation even though there is sufficient amount of stored energy in the dc link capacitor as shown in Fig. 4. Furthermore, the gradient of the dc link voltage  $d_{\rm vdc}/dt$  is directly proportional to the DVR-injected active power, i.e.,  $P_{\rm dvr}$ . The lower the value of  $P_{\rm dvr}$ , the smaller is the slope of the dc link voltage and the higher will be the time for which  $V_{\rm dvr}/n_t \leq (m_{i-{\rm max}}V_{\rm dc})/2$ . This leads to the following two hypotheses.

- The energy stored in the dc link capacitor can further be utilized.

- 2) The rate of change (fall) of the dc link voltage can further be optimized.

This brings another important variable in the power flow analysis which is the "maximum compensation time  $t_{c-\max}$ ." It is the direct measure of "useful" stored charge/energy in the dc link capacitor. The  $t_{c-\max}$  can be determined from the boundary condition of (12) and (14) as given in the following:

$$t_{c-\text{max}} = \frac{C * \left[ V_{\text{dc}}^2 - \left( \frac{2*V_{\text{dvr}}}{m_{i-\text{max}}*n_t} \right)^2 \right]}{2 * P_{\text{dvr}}}.$$

(15)

A detailed derivation of (15) is given in Appendix B. To increase  $t_{c-\max}$ , Meyer *et al.* suggested a method in [16] and [17] which decreases the injected voltage magnitude once the dc link voltage dropped to the threshold limit of (12) and allows further utilization of the dc link stored energy. However, as discussed in the introduction section, this method has no control on the injected active power and therefore is not the best choice for getting the maximum compensation time [18].

#### IV. PROPOSED COMPENSATION SCHEME

The work presented in this paper proposes an enhanced sag compensation method to extend the DVR compensation time. It optimizes the gradient of the dc link voltage  $(dv_{\rm dc}/dt)$  by regulating the amount of active power injected by DVR. In the proposed method, the controller restores both phase and

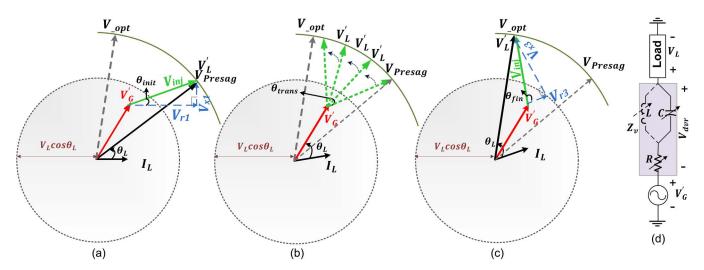

Fig. 5. Phasor diagram for the proposed sag compensation method. (a) Presag restoration, (b) intermediate transition, (c) final load voltage with MAP injection, and (d) DVR visualization as the variable virtual impedance changes from resistive to dominant capacitive (for sag) or inductive (for swell).

amplitude of the load voltage to the presag value and then initiates a transition toward the minimum active power (MAP) mode. The overall operation sequence and implementation of the proposed compensation method is discussed in the following subsections.

#### A. Phase Jump Detection and Presag Restoration

For detecting the phase jump, two PLLs are employed (one over the load voltage and another over the source voltage), giving  $\theta_{VL}$  and  $\theta_{Vg}$ , respectively. As soon as the sag is detected, the first step is to determine the DVR initial injection angle that avoids the phase jump at the load side. This is done by freezing the load voltage PLL that gives the presag angle  $(\theta_{VLp})$ . On the other hand, the unrestricted grid voltage PLL gives the grid voltage phase  $(\theta_{Vg})$ . The difference between these two angles gives the initial angle of injection

$$\theta_{\text{init}} = \theta_L + (\theta_{VLp} - \theta_{Vg})$$

$$= \theta_L + \delta$$

(16)

Note that, in the steady state, both angles will be identical, and thus, the difference will be zero. For sag detection, the absolute difference between the reference load voltage (1 p.u.) and the actual grid voltage (p.u.) in synchronous reference frame is calculated as follows [7], [19]–[22]:

$$\Delta V_{\text{sag}} = \left| 1 - \sqrt{V_{gd}^2 + V_{gq}^2} \right|. \tag{17}$$

As soon as  $\Delta V_{\rm sag} > 0.1$ , it is recognized as a voltage sag [23].

#### B. Controlled Transition Toward the MAP Mode

Once the presag voltage is successfully restored, after one cycle, a smooth transition toward the MAP mode is initiated and completed over the next one to two cycles. The final injection angle of DVR  $(\theta_{\rm fin})$  is given as

$$\theta_{\text{fin}} = \begin{cases} \frac{\pi}{2} + \gamma, & \text{if } \Delta V_{\text{sag}} \leq (1 - \cos \theta_L) \\ \pi - \tan^{-1} \left( \frac{V_L(\sin \theta_L)}{V_L \cos \theta_L - V_g'} \right), & \text{if } \Delta V_{\text{sag}} > (1 - \cos \theta_L) \end{cases}$$

(18)

A detailed derivation of (18) is given in Appendix C. The first part of (18) represents the self-supporting mode of operation in which the DVR absorbs active power (relatively very small amount) from the grid to overcome the system losses and thus maintains a constant voltage across the dc link capacitor. The term  $\gamma$  indicates the reduction in  $\theta_{\rm fin}$  due to loss component and is determined by the dc link (PI) controller. The second part of (18) represents a case where the self-supported dc link cannot be maintained due the constraint in (5). To ensure a smooth changeover, a transition ramp is defined between the initial and final operating points, as given in the following:

$$\theta_{\rm trans} = \theta_{\rm init} + \frac{\theta_{\rm fin} - \theta_{\rm init}}{\Delta T}(t)$$

(19)

where  $\Delta T$  determines the slope of the transition curve and is chosen as 30 ms.

#### C. Iterative Decrement in Injection Angle

In self-supporting mode, the DVR can compensate the sag for an indefinitely long time. However, for deeper sag depths, there is certain nonzero active power injected by DVR. This causes a reduction in the energy stored in the dc link capacitor, and consequently, its voltage reduces (gradually). To maintain the required voltage at the inverter output side, the controller increases the modulation index  $m_i$  until it reaches  $m_{i-\max}$ . This is the limiting case as explained by (12), beyond which the controller goes into overmodulation and cannot maintain the rated load voltage. To avoid this overmodulation condition, an iterative control loop is used, which constantly monitors the dc link voltage and decreases  $\theta_{\rm fin}$  in (18) to keep  $V_{\rm dc} > V_{\rm dc-min}$  and is given as

$$\theta_{\rm fin} = \theta_{\rm fin} - \epsilon \tag{20}$$

where  $\epsilon$  is chosen as 0.01 rad.

#### D. Operation Sequence

Fig. 5(a)–(c) depicts the overall operation sequence of the proposed phase jump compensation scheme. The transition

| TABLE I                 |                      |  |

|-------------------------|----------------------|--|

| DVR SYSTEM PARAMETERS ( | BOUNDARY CONDITIONS) |  |

| Parameter                                  | Value            |

|--------------------------------------------|------------------|

| Grid voltage (L-L) (rms) V <sub>base</sub> | 415 V            |

| Line frequency                             | 50 Hz            |

| Nominal Power (Base kVA)                   | 10 kVA           |

| Nominal Load power factor                  | 0.7 Lagging      |

| Maximum compensation time                  | 10 cycles        |

| Maximum sag depth                          | 0.5 p.u          |

| Maximum phase jump                         | ±45 <sup>0</sup> |

| Maximum injected voltage                   | 0.7 p.u          |

| Transformer turns ratio                    | 1:1              |

| DC link Capacitance value                  | 9000 μF          |

from high active power mode (presag) to MAP mode is shown in three steps. The illustration is for the case where the sag depth is more than the limit in (5) and there is a positive phase jump associated with the sag. As discussed previously and shown in Fig. 5(a), DVR initiates the compensation by supplying high active power to the load  $(V_{r1} \gg V_{x1})$  and restores both magnitude and phase of the load voltage to presag values. After one cycle, the transition toward the MAP mode is initiated, and DVR gradually increases the contribution of reactive power. As seen from Fig. 5(b) and (c), the injected voltage magnitude and its phase angle are gradually increasing until  $V_L'$  reaches  $V_{L-\text{opt}}$ . Note that at the final operating point  $V_{r1} \ll V_{x1}$ . The aforementioned DVR operation can be viewed as an equivalent variable impedance  $Z_v$  where the operation begins with dominant resistive impedance  $Z_v = R$  (high active power) and completes as dominant capacitive impedance  $Z_{\nu} \approx X_{C}$ (high reactive power).

### V. ANALYTICAL STUDY ON COMPENSATION TIME WITH DIFFERENT APPROACHES

In this section, a comparative study is presented to determine the maximum compensation time achieved using the aforementioned phase jump compensation methods. These include the following: 1) the presag; 2) the method given in [16], named as presag—in-phase in this paper; and 3) the proposed method. Table I shows the various design parameters used for the comparison. The maximum compensation time of 200 ms (10 cycles) with a phase jump of  $+45^{\circ}$  is taken as reference. Using (15), the value of the dc link capacitor is obtained as  $9000~\mu F$ .

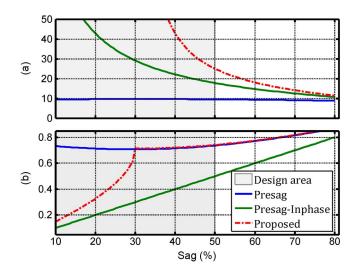

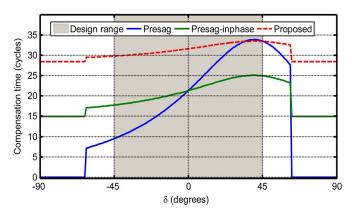

The sag depth is varied over a range of values from 10% to 80% of nominal grid voltage, keeping the power factor and phase jump fixed at 0.7 lagging and  $+45^\circ$ , respectively. Analytically computed DVR-injected magnitude and maximum compensation times are provided in Fig. 6. Note that the DVR voltage magnitudes are shown after the first one cycle of compensation as all of the three methods perform identically for the first cycle. As seen from Fig. 6(b), both the presag and proposed methods have the same  $V_{\rm DVR}$  magnitude for a sag depth greater than the limit in (6), i.e., 30%. However, as noticed from Fig. 6(a),  $t_{c-{\rm max}}$  is highest for the proposed method for all values of sag depths. For the designed range of

Fig. 6. Maximum compensation time and DVR-injected voltage for various sag depths with different methods. (a) Compensation time cycles. (b)  $\rm V_{\rm DVR}$  p.u.

Fig. 7. Maximum compensation time for a range of variation in phase iump.

50% sag depth, it can be seen that the presag—in-phase method improves the compensation time from 10 to 16 cycles over the presag method. The proposed method further improves it to 22 cycles. Moreover, for the sag depth lower than 30%, the proposed method can withstand any sag duration by operating in the self-supporting mode. The significant improvement in the compensation time is due to the least possible utilization of dc link active power, thus resulting in the slowest discharging of the dc link capacitor. Note that the proposed method does not result in higher injection voltage magnitude than the design limit of 0.7 p.u., which is clear in Fig. 6(b).

Fig. 7 depicts the scenario where the phase jump is varied from  $-90^{\circ}$  to  $+90^{\circ}$  for a sag depth of 0.5 p.u. and other boundary conditions from Table I. As seen from the graph, the maximum compensation time is highest for the proposed method. It can also be noted that the presag method becomes unable to correct the phase jump beyond  $-60^{\circ}$  and  $+60^{\circ}$  due to violation of (12).

#### VI. OVERALL DVR SYSTEM CONTROL SCHEME

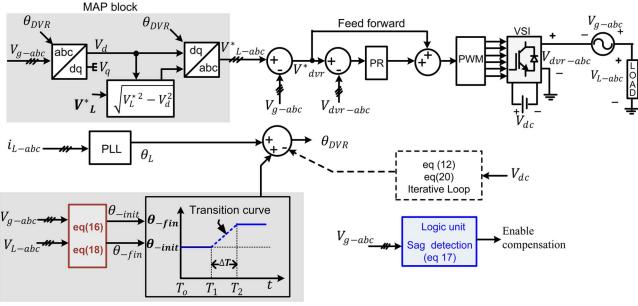

Fig. 8 depicts the detailed block diagram of the proposed phase jump compensation method. A logic unit is employed to

Phase jump detection block

Fig. 8. Detailed block diagram of the proposed phase jump compensation method with MAP injection.

constantly monitor the grid voltage for sag detection using (17). To obtain the reference load voltage, the control system is divided into two submodules: 1) phase jump detection plus DVR injection angle calculation and (2) MAP injection. To achieve a decoupled active and reactive power control, the phase of the line current is considered as the reference and is obtained by the PLL. The phase jump detection block computes the DVR initial (presag injection) angle and final (MAP injection) angle. Once the transition is over, the MAP block gives the reference voltage  $V_{L-abc}^* = V_{\text{opt}}$ . As shown in Fig. 8, the obtained DVR reference voltage  $V_{

m dyr}^*$  is compared with the actual voltage in the stationary reference frame. A proportional-resonant (PR) controller with a large gain at the grid fundamental frequency is used for accurate tracking of  $V_{

m dvr}^*$ . To compensate for DVR system losses,  $V_{

m dvr}^*$  is added as a feedforward signal to the output of the PR controller. The dc link voltage is constantly monitored in an iterative control loop to regulate the injected voltage angle, thus avoiding overmodulation. Note that this block is only required when the sag depth is close to the system design limit.

#### VII. EVALUATION

The effectiveness of the proposed method is evaluated through MATLAB/Simulink-based simulation study and, lastly, validated on a scaled laboratory prototype experimentally.

#### A. Simulation Study

A simulation model for the DVR system, with the parameter given in Table I, is developed and simulated for the performance evaluation. The dc link capacitor of 9000  $\mu F$ , as computed in the previous section, is used for this study. As the intention is to maintain the rated voltage across the load terminals without any phase jump, the sensitive load is represented by an R-L load.

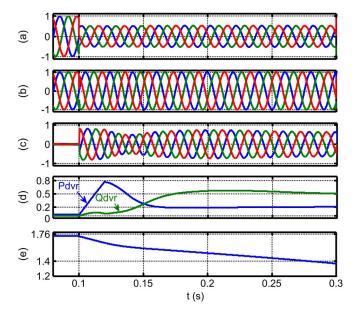

Fig. 9. Simulation results for the proposed sag compensation method for 50% sag depth. (a) PCC voltage. (b) Load voltage. (c) DVR voltage. (d) DVR active and reactive power. (e) DC link voltage.

The simulation results for two different scenarios are given in Figs. 9 and 10. In the first scenario, a sag depth of 50% [higher than the limit in (5)] is considered with a phase jump of  $+25^{\circ}$ . A symmetrical voltage sag, for ten cycles, is initiated at time t=0.1 s [Fig. 9(a)]. As noticed from Fig. 9(b), the load does not see any change in the voltage phase or magnitude. The DVR-injected voltage and active–reactive power profiles are shown in Fig. 9(c) and (d), respectively. It can be noticed that the DVR restores the phase jump by injecting the maximum active power at the beginning, and the controller gradually shifts to the MAP mode after one cycle. Fig. 9(e) shows a constant drop in dc link voltage; however, once the controller goes into MAP mode, a slower fall rate can be noticed.

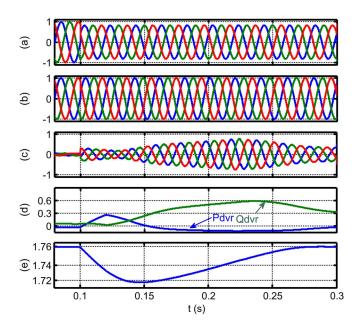

Fig. 10. Simulation results for the proposed sag compensation method for 23% sag depth. (a) PCC voltage. (b) Load voltage. (c) DVR voltage. (d) DVR active and reactive power. (e) DC link voltage.

In the second scenario, a sag depth of 23% [lower than the limit given in (5)] is considered with a phase jump of  $+25^\circ$ . As seen from the results in Fig. 10, the DVR successfully compensates the load voltage phase and magnitude with the proposed method. Since the voltage sag depth is lower than the limit in (5), the controller settles in the self-supporting mode. A reduction in dc link voltage can be seen [Fig. 10(e)] during the first two cycles (phase jump restoration plus transition period), but as the controller moves into self-supporting mode, the dc link voltage is regulated back to the reference value. This can be noticed from Fig. 10(d) as well, where the injected active power is positive for the first two cycles and negative onward (self-supporting mode).

Furthermore, the study was extended to compute the maximum achievable compensation time, for the existing system, with the proposed method. It is found that the compensation time can be extended from 10 to 25 cycles for the worst case scenario. Further enhancement in compensation time (more than 25 cycles) will be achieved for intermediate sag depths. Additionally, based on the designed criteria of ten cycles for the new installation, the proposed method can reduce the dc link capacitor size from 9000 to 4200  $\mu \rm F$  (details given in Appendix C).

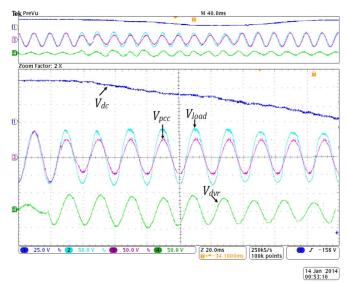

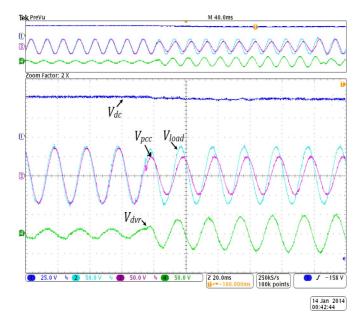

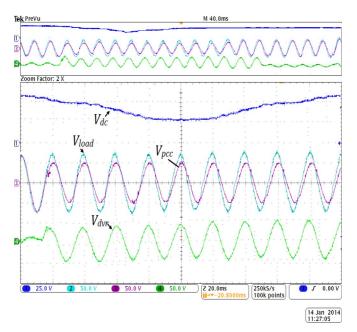

#### B. Experimental Validation

A scaled experimental prototype is developed using digital signal processor (DSP) DS1103 dSPACE and Semikron AN 8005 VSI. The experimental system data are given in Table II. The DSP sampling time of 40  $\mu s$  is used to run the algorithm in real time. Using the programmable voltage source, a sag depth of 35% with  $+25^{\circ}$  jump in the voltage phase is initiated. The experimental results for different sag compensation schemes are given in Figs. 11–13.

| Source<br>Chroma 61703 | Supply voltage: 50 V-rms, 50 Hz Source Impedance: $R_g=0.047~\Omega$ and $L_g=160~\mu H$                                                                                         |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVR                    | DC link capacitors, $C_{dc} = 1100 \mu\text{F}$<br>Reference DC link voltage = 55 V<br>Filter inductor, $L_f = 5 \text{mH}  C_f = 50 \mu\text{F}$<br>Transformer turns ratio 1:1 |

| Load                   | $R = 11 \Omega$ and $L = 80 \text{ mH}$<br>Nominal Load voltage = 50 V<br>Rating = 250 W                                                                                         |

| Compensation time      | 10 cycles (200 ms)                                                                                                                                                               |

Fig. 11. Experimental results for 35% sag depth with  $+25^\circ$  phase jump using the presag compensation method.

Fig. 12. Experimental results for 35% sag depth with  $+25^\circ$  phase jump using the quadrature injection method.

Fig. 13. Experimental results for 35% sag depth with  $+25^{\circ}$  phase jump using the proposed method.

Fig. 11 shows the performance of the presag method. It can be seen that the load voltage does not see any transient in the magnitude as well as phase. However, due to the active power injection, there is rapid reduction in the dc link voltage. After seven cycles (lower cycles due to the losses associated with the DVR system), the dc link voltage is dropped to less than 15 V, which consequently decreases the injected voltage magnitude, and as a result, DVR fails to maintain the rated load voltage. For the same sag condition, the performance of the quadrature injection method is given in Fig. 12. The phase jump goes uncompensated; however, it compensates the sag, effectively maintaining the load voltage at rated value while regulating the dc link voltage. Finally, Fig. 13 demonstrates the performance of the proposed method.

As viewed from Fig. 13, the DVR begins compensation by restoring the load voltage and phase to the presag values. There is reduction in dc link voltage due to the requirement of active power for phase jump compensation. Note that the first stage is temporary and lasts for two cycles (after compensation begins). After the first two cycles (from Fig. 13), the proposed controller initiates the transition towards MAP (in this case, toward selfsupporting mode since  $\Delta V_{\rm sag} \leq (1 - \cos \theta_L)$ ). This transition (discussed in Fig. 5) can be confirmed by observing the relative phase angle difference between the source and load voltage waveforms. The corresponding increase in the injected voltage magnitude and slow fall rate of the dc link voltage can also be observed. This intermediate transition stage lasts for another two and half cycles. Finally, the proposed controller proceeds to operate in the self-supporting mode to gradually restore the dc link voltage back to the reference value. The corresponding increase in the injected voltage magnitude to recover the dc link voltage can also be noticed from Fig. 13.

The aforementioned experimental investigation effectively demonstrates the applicability and feasibility of the proposed phase jump compensation method that can extend the compensation duration of DVR.

#### VIII. CONCLUSION

In this paper, an enhanced sag compensation scheme has been proposed for the capacitor-supported DVR. The proposed strategy improves the voltage quality of sensitive loads by protecting them against the grid voltage sags involving the phase jump. It also increases compensation time by operating in MAP mode through a controlled transition once the phase jump is compensated. To illustrate the effectiveness of the proposed method, an analytical comparison has been carried out with the existing phase jump compensation schemes. It is shown that the compensation time can be extended from 10 to 25 cycles (considering presag injection as the reference method) for the designed limit of 50% sag depth with 45° phase jump. Further extension in compensation time can be achieved for intermediate sag depths. This extended compensation time can be seen as a considerable reduction in dc link capacitor size (for the studied case more than 50%) for the new installation. The effectiveness of the proposed method has been evaluated through extensive simulations in MATLAB/Simulink and validated on a scaled laboratory prototype experimentally. The experimental results demonstrate the feasibility of the proposed phase jump compensation method for practical applications.

## $\begin{array}{c} \text{APPENDIX A} \\ \text{DERIVATION OF } P_{\mathrm{presag}} \text{ IN (11)} \end{array}$

Defining the per unit value of sag depth  $\Delta V_{\rm sag}$  as

$$\Delta V_{\text{sag}} = \frac{V_L - V_G'}{V_L} \tag{A1}$$

the injected voltage in (9) can be expressed as a function of the sag depth  $\Delta V_{\rm sag}$

$$V_{\rm DVR} = \sqrt{2} V_L \sqrt{\Delta V_{\rm sag}^2 + 2(1 - \Delta V_{\rm sag}) - 2(1 - \Delta V_{\rm sag}) \cos(\delta)}. \tag{A2} \label{eq:A2}$$

The active power supplied by DVR during presag injection can be expressed as

$$P_{\text{presag}} = P_{\text{Load}} - P_{\text{GRID}} = \sqrt{3}V_L I_L \cos \theta_L$$

$$-\sqrt{3}V_G' I_L \cos(\theta_L - \delta) \tag{A3}$$

$$P_{\text{presag}} = \sqrt{3}V_L I_L(\cos(\theta_L)) - (1 - \Delta V_{\text{sag}})\cos(\theta_L - \delta). \tag{A4}$$

## $\begin{array}{c} {\sf APPENDIX\ B} \\ {\sf DERIVATION\ OF\ Maximum\ Compensation} \\ {\sf TIME\ } t_{c-\max}\ {\sf IN\ (15)} \end{array}$

The power flow out of the dc link capacitor in the steady state is given as

$$P_{c-\text{dc}} = \frac{1}{2} C_{\text{dc}} \frac{d}{dt} \left( v_{\text{dc}}^2 \right). \tag{B1}$$

Due to active power flow, there is a reduction in dc link voltage from the reference value  $V_{\rm dc-ref}$ . As shown in Fig. 4,

Fig. 14. DVR final injection angle for the proposed method for per sag depth (a) less than  $1-\cos\theta_L$  and (b) greater than  $1-\cos\theta_L$ .

the voltage drop continues until the dc link voltage reaches  $V_{\rm dc-min}$ , which is given by

$$V_{\text{dc-min}} = \frac{\frac{2V_{\text{DVR}}}{n_t}}{m_{i-\text{max}}}.$$

(B2)

The total active power supplied by the dc link capacitor during this time  $\Delta T$  is given by

$$P_{c-\text{dc}} = \frac{1}{2} C_{\text{dc}} \frac{\Delta V_{\text{dc}}^2}{\Delta T} = \frac{1}{2} C_{\text{dc}} \left( \frac{V_{\text{dc-ref}}^2 - V_{\text{dc-min}}^2}{\Delta T} \right) \quad (B3)$$

$$\Delta T = t_{c-\text{max}} - t_{c-\text{min}} \tag{B4}$$

where  $t_{c-\max}$  and  $t_{c-\min}$  are the maximum and minimum compensation time intervals, respectively. Considering  $t_{c-\min}=0$  in (B4) and substituting the value of  $\Delta T$  and  $V_{dc-\min}$  from (B4) and (B2), respectively, into (B3), the following relation is obtained:

$$P_{c-\text{dc}} = \frac{1}{2} C_{\text{dc}} \frac{\left(V_{\text{dc-ref}}^2 - \left(\frac{\frac{2*V_{\text{DVR}}}{n_t}}{m_{i-\text{max}}}\right)^2\right)}{t_{c-\text{max}}}.$$

(B5)

Equating the dc link power  $P_{c-{

m dc}}$  to the active power injected by DVR in various compensation methods and rearranging (B5) for  $t_{c-{

m max}}$ , the relationship in (15) can be obtained. The value of the dc link capacitance for the boundary conditions of Table I can be obtained as follows:

$$C_{\text{dc}} = \frac{2\int_{t=0}^{t_1} P_1 t \, dt}{V_{\text{dc-ref}}^2 - \left(\frac{2V_1}{m_i}\right)^2} + \frac{2\int_{t=t_1}^{t_2} P_2 t \, dt}{V_{\text{dc-ref}}^2 - \left(\frac{2V_2}{m_i}\right)^2} + \frac{2\int_{t=t_2}^{\text{Tmax}} P_3 t \, dt}{V_{\text{dc-ref}}^2 - \left(\frac{2V_3}{m_i}\right)^2}$$

(B6)

where  $P_1 = P_{\rm presag}$ ,  $P_2 = \sqrt{3}V_LI_L(\cos(\theta_L) - 1 + \Delta V_{\rm sag})$ , and  $P_3 = \sqrt{3}V_LI_L(\cos(\theta_L)\Delta V_{\rm sag})$ . Substituting the system parameters from Table I in (B6), the dc link capacitance for the proposed method is calculated to be 4200  $\mu$ F.

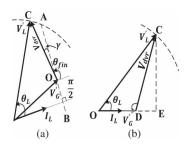

## APPENDIX C DERIVATION OF $heta_{ m fin}$ IN (18)

The final angle of DVR injection depends on the magnitude of sag depth  $\Delta V_{\rm sag}$ . If  $\Delta V_{\rm sag} \leq (1-\cos\theta_L)$ , the DVR operates in self-supporting mode as shown in Fig. 14(a). The

final injection angle  $\theta_{\rm fin}$  can be observed from Fig. 14(a) as mentioned in the following:

$$\theta_{\rm fin} = \frac{\pi}{2} + \gamma. \tag{C1}$$

The displacement angle  $\gamma = \angle AOC$  indicates that DVR is not operating in quadrature injection mode, i.e., there is an active power flow between the grid and the DVR given by

$$P_d = \sqrt{3}V_{\rm DVR}I_L\cos\left(\frac{\pi}{2} + \gamma\right). \tag{C2}$$

Fig. 14(b) shows the second scenario where  $\Delta V_{\rm sag} \geq (1-\cos\theta_L)$ . In this case, DVR operates in the MAP mode. The final injection angle  $\angle ODC$  can be calculated from Fig. 14(b) as follows:

$$\angle ODC = \pi - \tan^{-1}\left(\frac{CE}{DE}\right) = \tan^{-1}\left(\frac{CE}{OE - OD}\right).$$

(C3)

Putting  $CE = V_L(\sin \theta_L)$ ,  $OE = V_L(\cos \theta_L)$ , and  $OD = V_G'$ , the final injection angle in (18) can be obtained

$$\angle ODC = \theta_{\text{fin}} = \pi - \tan^{-1} \left( \frac{V_L(\sin \theta_L)}{V_L \cos \theta_L - V_G'} \right).$$

(C4)

#### REFERENCES

- [1] J. A. Martinez and J. M. Arnedo, "Voltage sag studies in distribution networks—Part I: System modeling," *IEEE Trans. Power Del.*, vol. 21, no. 3, pp. 338–345, Jul. 2006.

- [2] J. G. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer, compensating voltage sags with phase jump," in *Proc. IEEE APEC Expo.*, 2001, pp. 1267–1273.

- [3] J. D. Li, S. S. Choi, and D. M. Vilathgamuwa, "Impact of voltage phase jump on loads and its mitigation," in *Proc. 4th Int. Power Electron. Motion Control Conf.*, Xi'an, China, Aug. 14–16, 2004, vol. 3, pp. 1762–1176.

- [4] M. Sullivan, T. Vardell, and M. Johnson, "Power interruption costs to industrial and commercial consumers of electricity," *IEEE Trans. Ind. Appl.*, vol. 33, no. 6, pp. 1448–1458, Nov./Dec. 1997.

- [5] J. Kaniewski, Z. Fedyczak, and G. Benysek, "AC voltage sag/swell compensator based on three-phase hybrid transformer with buck-boost matrix-reactance chopper," *IEEE Trans. Ind. Electron.*, vol. 61, no. 8, pp. 3835–3846, Aug. 2014.

- [6] M. Castilla, J. Miret, A. Camacho, J. Matas, and L. de Vicuna, "Voltage support control strategies for static synchronous compensators under unbalanced voltage sags," *IEEE Trans. Ind. Electron.*, vol. 61, no. 2, pp. 808–820, Feb. 2014.

- [7] P. M. Garcia, F. Mancilla, and J. M. Ramirez, "Per-sequence vector-switching matrix converter modules for voltage regulation," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5411–5421, Dec. 2013.

- [8] C. Kumar and M. Mishra, "A multifunctional DSTATCOM operating under stiff source," *IEEE Trans. Ind Electron.*, vol. 61, no. 7, pp. 3131– 3136, Jul. 2014.

- [9] P. Kanjiya, B. Singh, A. Chandra, and K. Al-Haddad, "SRF theory revisited to control self-supported dynamic voltage restorer (DVR) for unbalanced and nonlinear loads," *IEEE Trans. Ind. Appl.*, vol. 49, no. 5, pp. 2330–2340, Sep./Oct. 2013.

- [10] C. Wessels, F. Gebhardt, and F. W. Fuchs, "Fault ride-through of a DFIG wind turbine using a dynamic voltage restorer during symmetrical and asymmetrical grid faults," *IEEE Trans. Power Electron.*, vol. 26, no. 3, pp. 807–815, Mar. 2011.

- [11] Y. W. Li, D. M. Vilathgamuwa, F. Blaabjerg, and P. C. Loh, "A robust control scheme for medium-voltage-level DVR implementation," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2249–2261, Aug. 2007.

- [12] A. K. Sadigh and K. M. Smedley, "Review of voltage compensation methods in dynamic voltage restorer (DVR)," in *Proc. IEEE Power Energy Soc. Gen. Meet.*, Jul. 2012, pp. 1–8.

- [13] J. G. Nielsen and F. Blaabjerg, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump," in *Proc. IEEE Annu. Appl. Power Electron. Conf. Expo.*, 2001, no. 2, pp. 1267–1273.

- [14] H. K. Al-Hadidi, A. M. Gole, and D. A. Jacobson, "A novel configuration for a cascade inverter based dynamic voltage restorer with reduced energy storage requirements," *IEEE Trans. Power Del.*, vol. 23, no. 2, pp. 881– 888, Apr. 2008.

- [15] H. K. Al-Hadidi, A. M. Gole, and D. A. Jacobson, "Minimum power operation of cascade inverter-based dynamic voltage restorer," *IEEE Trans. Power Del.*, vol. 23, no. 2, pp. 889–898, Apr. 2008.

- [16] C. Meyer, R. W. Doncker, Y. W. Li, and F. Blaabjerg, "Experimental verification of an optimized control strategy for a medium-voltage DVR," in *Proc. 36th IEEE PESC*, 2006, pp. 1–7.

- [17] C. Meyer, R. W. Doncker, Y. W. Li, and F. Blaabjerg, "Optimized control strategy for a medium-voltage DVR—Theoretical investigations and experimental results," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2746– 2754. Nov. 2008.

- [18] T. M. Undeland, W. P. Robbins, and N. Mohan, Power Electronics Converters, Applications and Design. New York, NY, USA: Wiley, 2003.

- [19] C. Fitzer, M. Barnes, and P. Green, "Voltage sag detection technique for a dynamic voltage restorer," *IEEE Trans. Ind. Appl.*, vol. 40, no. 1, pp. 203– 212, Jan./Feb. 2004.

- [20] T. Jimichi, H. Fujita, and H. Akagi, "Design and experimentation of a dynamic voltage restorer capable of significantly reducing an energystorage element," *IEEE Trans. Ind. Appl.*, vol. 44, no. 3, pp. 817–825, May/Jun. 2008.

- [21] H. Igarashi and H. Akagi, "System configurations and operating performance of a dynamic voltage restorer," *IEEJ Trans. Ind. Appl.*, vol. 123, no. 9, pp. 1021–1028, Sep. 2003.

- [22] L. Yong, X. Guochun, L. Bo, W. Xuanlv, and Z. Sihan, "A transformerless active voltage quality regulator with the parasitic boost circuit," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1746–1756, Apr. 2014.

- [23] A. Prasai and D. M. Divan, "Zero-energy sag correctors—Optimizing dynamic voltage restorers for industrial applications," *IEEE Trans. Ind. Appl.*, vol. 44, no. 6, pp. 1777–1784, Nov./Dec. 2008.

Abdul Mannan Rauf received the B.Sc. degree from the University of Engineering and Technology Taxila, Taxila, Pakistan, in 2009 and the M.Sc. degree in electrical engineering from Masdar Institute of Science and Technology, Abu Dhabi, United Arab Emirates, in 2014.

Since August 2014, he has been a Research Engineer with Masdar Institute of Science and Technology. His research interests include power electronics, power quality enhancement, and grid integration of inverter-

based renewable-energy systems.

Vinod Khadkikar (S'06–M'09) received the B.E. degree in electrical engineering from the Government College of Engineering, Dr. Babasaheb Ambedkar Marathwada University, Aurangabad, India, in 2000, the M.Tech. degree in electrical engineering from the Indian in 2002, and the Ph.D. degree in electrical engineering from the École de Technologie Supérieure (ETS), Montréal, QC, Canada, in 2008.

From December 2008 to March 2010, he was a Postdoctoral Fellow with the University of Western Ontario, London, ON, Canada. From April 2010 to December 2010, he was a visiting faculty member at the Massachusetts Institute of Technology, Cambridge, MA, USA. He is currently an Associate Professor with Masdar Institute of Science and Technology, Abu Dhabi, United Arab Emirates. He is currently an Associate Editor of *IET Power Electronics*. His research interests include applications of power electronics in distribution systems and renewable-energy resources, grid interconnection issues, power quality enhancement, active power filters, and electric vehicles.