# A Quad Two-Level Inverter Configuration for Four-Pole Induction-Motor Drive with Single DC Link

Kiran Kumar N. and K. Sivakumar, Member, IEEE

Abstract—A multilevel inverter topology for a four-pole induction-motor drive is presented in this paper, which is constructed using the induction-motor stator winding arrangement. A single dc source with a less magnitude when compared with conventional five-level inverter topologies is used in this topology. Therefore, power balancing issues (which are major challenges in conventional multilevel inverters) are minimized. As this configuration uses a single dc source, it provides a path for zero-sequence currents because of the zero-sequence voltages present in the output, which will flow through the motor phase winding and power electronic switches. To minimize these zero-sequence currents, sine-triangle pulsewidth modulation (SPWM) is used, which will shift the lower order harmonics near to switching frequency in the linear modulation region. However, in the case of overmodulation, harmonic voltages will be introduced close to the fundamental frequency. In this regard, a modified SPWM technique is proposed in this paper to operate the drive in the overmodulation region up to the modulation index of  $2/\sqrt{3}$ . The proposed quad two-level inverter topology is experimentally verified with a laboratory prototype on a four-pole 5-hp induction motor. Experimental results show the effectiveness of the proposed topology in the complete linear modulation region and the overmodulation region.

Index Terms—Induction-motor drive, modified sinetriangle pulsewidth modulation (SPWM), multilevel inverter, overmodulation.

## NOMENCLATURE

| <b>IVPWC</b>                       | Identical voltage profile winding coil. |

|------------------------------------|-----------------------------------------|

| SPWM                               | Sine-triangle pulsewidth modulation.    |

| $i_{\rm as},i_{\rm bs},i_{\rm cs}$ | Stator phase currents.                  |

| $r_{ m s}$                         | Stator resistance.                      |

| $r_{ m r}$                         | Rotor resistance.                       |

| $L_{ m ls}$                        | Stator leakage inductance.              |

| $L_{\rm ss}$                       | Stator self-inductance.                 |

| $L_{ m lr}$                        | Rotor leakage inductance.               |

| $L_{ m rr}$                        | Rotor self-inductance.                  |

| $L_{ m m}$                         | Magnetizing inductance.                 |

| $\Re$                              | Reluctance.                             |

| l                                  | Mean length.                            |

| A                                  | Area of the core.                       |

|                                    | 5                                       |

Manuscript received January 11, 2014; revised March 26, 2014 and April 30, 2014; accepted May 3, 3014. Date of publication May 30, 2014; date of current version December 19, 2014.

The authors are with the Indian Institute of Technology Hyderabad, Hyderabad 502205, India (e-mail: ksiva@iith.ac.in).

Digital Object Identifier 10.1109/TIE.2014.2327577

Permeability.

mi Modulation index. p (d/dt).

#### I. INTRODUCTION

ULTILEVEL inverter technology has been widely used for the control of medium- and high-voltage ac drive applications from the past few decades [1] because of its improved output voltage quality [2], better harmonic performance [3], less voltage stress on power electronic devices [4], and so on. The basic concept of multilevel inverters is to achieve the staircase voltage waveform by using more low-rated power electronic switches and voltage sources. As the number of output voltage levels increase, the requirement of series-connected switches will also increase in the case of conventional multilevel inverters such as diode-clamped and flying-capacitor (FC) multilevel inverters. Therefore, if any of the switches fails, the entire topology has to be shut down [5], [6], resulting in decreased system reliability. Moreover, these topologies have some inherent drawbacks such as neutral-point voltage balancing [7] and capacitor voltage balancing [8] problems, which in turn cause unequal voltage sharing across the switches and adds dc offset voltage to the output voltage waveform. Therefore, special capacitor voltage balancing techniques are needed to eliminate these issues [9]. The reliability of the system can be increased using the H-bridge configuration, as presented in [10], which will also eliminate the capacitor voltage balancing issue and the neutral-point voltage balancing issue. However, as the number of voltage levels increase, it requires more isolated dc sources [11]. Another interesting topology to increase the reliability of the system is the dual-inverter configuration using an open-end winding induction motor [12]–[14]. In this configuration, the neutral point of the induction motor is disconnected, and both sides of the winding are fed from two twolevel (or multilevel) inverters [15]. This configuration requires only half of the dc source voltage when compared with conventional neutral-point-clamped (NPC) or FC multilevel inverters. To eliminate the aforementioned problems, such as capacitor voltage balancing and the requirement of more voltage sources, a five-level inverter topology is presented in [15], which uses three dc sources to obtain a five-level voltage waveform. In this paper, the advantage of two IVPWCs [15]-[17] of a fourpole induction motor is used in designing the multilevel inverter topology.

On the other hand, an open-end winding induction motor supplied by a SVPWM-controlled multilevel inverters with a single dc source will provide path for the zero-sequence currents [18]–[20], [25] because of the dominant lower order harmonic voltages in the inverter output voltage. A five-level inverter topology for a four-pole induction-motor drive with a single dc link is presented in [17], which has used SPWM to minimize the zero-sequence currents though the motor phase windings. However, this scheme is effective in the linear modulation only.

In this paper, a modified SPWM technique is proposed to operate the five-level inverter configuration (using quad two-level inverters) also in overmodulation region. The proposed scheme is experimentally verified with a laboratory prototype, and results are then presented.

# II. VOLTAGE EQUATIONS OF INDUCTION-MOTOR STATOR WINDING

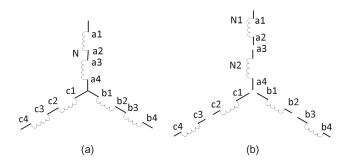

It is well known that, in a conventional ac machine, the winding coils which are 360° (electrical) apart will have identical voltage profiles across them. Thus, the four-pole induction motor consists of two IVPWCs (where the number of IVPWCs is equal to the number of pole pairs) [15]. In the conventional four-pole induction motor, these two windings are connected in series, as shown in Fig. 1(a). However, in this paper, these are disconnected, as shown in Fig. 1(b). As the two windings are disconnected exactly with an equal number of turns, it can be written [as shown in Fig. 1(a) and (b)] as

$$N_1 = N_2 = \frac{N}{2}. (1)$$

Reluctance is given by [22]

$$\Re = \frac{l}{\mu A}.\tag{2}$$

The following observations can be made when compared with conventional-induction-motor parameters.

- a) Stator resistance  $(r_s = \rho l/A)$  will be half because the length of the copper is half.

- b) Reluctance offered to the leakage flux will be half because the mean length of the stator leakage flux is half; hence, from (1) and (2), the leakage inductance  $(L_{1\rm ls}=N_1^2/\Re)$  will be half.

- c) Reluctance offered to the magnetizing flux will be the same because the mean length of the core is the same in both cases. Therefore, from (1) and (2), the magnetizing inductance ( $L_{\rm ms}=N_1N_2/\Re$ ) will be 1/4 times [22].

From the above discussion and by writing KVL shown in Fig. 1(b), the voltage across one IVPWC of A-phase can be obtained as

$$V_{a1} - V_{a2} = \left(\frac{r_s}{2}\right) i_{as} + \left(\frac{L_{ss}}{2}\right) p i_{as}$$

$$-\left(\frac{1}{2}\right) \left(\frac{L_m}{2}\right) p i_{bs} - \left(\frac{1}{2}\right) \left(\frac{L_m}{2}\right) p i_{cs}. \tag{3}$$

The voltage across the other IVPWC of A-phase can be obtained by writing Kirchoff's voltage law (KVL) shown in Fig. 1(b), i.e.,

$$V_{a3} - V_{a4} = \left(\frac{r_{s}}{2}\right) i_{as} + \left(\frac{L_{ss}}{2}\right) p i_{as}$$

$$-\left(\frac{1}{2}\right) \left(\frac{L_{m}}{2}\right) p i_{bs} - \left(\frac{1}{2}\right) \left(\frac{L_{m}}{2}\right) p i_{cs}. \tag{4}$$

Fig. 1. Induction motor stator winding. (a) General arrangement. (b) Arrangement for the proposed inverter.

The effective voltage across the stator winding is the sum of the voltages across the two individual windings, i.e.,

$$V_{\rm as} = (V_{\rm a1} - V_{\rm a2}) + (V_{\rm a3} - V_{\rm a4}). \tag{5}$$

The motor phase voltage can be achieved by substituting (3) and (4) into (5) as follows:

$$V_{\rm as} = r_{\rm s}i_{\rm as} + L_{\rm ss}pi_{\rm as} - \left(\frac{1}{2}\right)L_{m}pi_{\rm bs} - \left(\frac{1}{2}\right)L_{m}pi_{\rm cs}.$$

(6)

The voltage across the total winding of A-phase can be obtained by writing the KVL shown in Fig. 1(a), which is equal to the (6).

It can be observed from the above discussion that (6) and the voltage equation of the conventional induction motor presented in [22] are identical.

# III. PROPOSED MULTILEVEL INVERTER TOPOLOGY

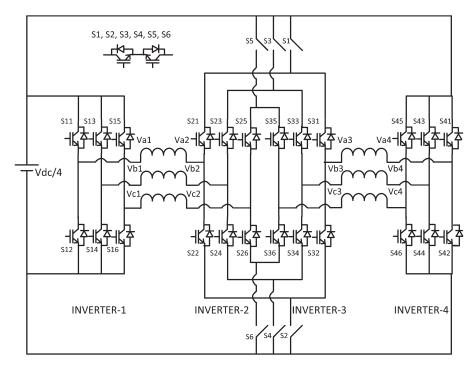

The five-level inverter topology presented in [15] uses three dc sources to obtain a five-level voltage waveform. Mostly diode bridge rectifiers are used for providing dc supply. Therefore, in regenerative braking, it requires three braking rheostats and three control mechanisms to protect the rectifier units, which complicate control and power circuits. In this paper, three dc sources are replaced by a single dc source, as shown in Fig. 2. The two disconnected IVPWCs are supplied with four conventional two-level inverters, and all of them are connected to the same dc source, as shown in Fig. 2. The maximum voltage blocking capacity of all two-level inverter switches is equal to input dc source voltage  $(v_{\rm dc}/4)$ . Two switches in the same leg of the two-level inverters complements each other.  $S_1$  to  $S_6$  are bidirectional (four-quadrant) switches that can allow the current in both directions and can block the voltage in both directions. The maximum voltage blocking capacity of these switches is  $v_{\rm dc}/8$  only. All these (main and auxiliary) switches are switched in such a way that it produces five-level voltage  $((v_{dc}/2), (v_{dc}/4), 0, (-v_{dc}/4), (-v_{dc}/2))$  across the motor phase winding, and the possible switching combinations are shown in Table I. Permanent shorting of the bidirectional switches cause unequal voltages across IVPWCs during some  $((-v_{\rm dc}/4),0,(v_{\rm dc}/4))$  voltage-level synthesis. Hence, control of these bidirectional switches is important, which is explained clearly in [17].

The proposed multilevel inverter topology is compared with the conventional five-level NPC inverter, FC inverter, and

Fig. 2. Proposed multilevel inverter topology.

TABLE I

POSSIBLE SWITCHING COMBINATIONS TO GENERATE

FIVE-LEVEL VOLTAGE WAVEFORMS

| Voltage Magnitude   | S <sub>11</sub> | S <sub>21</sub> | S <sub>31</sub> | S <sub>41</sub> | $S_1$ | S <sub>2</sub> |

|---------------------|-----------------|-----------------|-----------------|-----------------|-------|----------------|

| $+\frac{V_{dc}}{2}$ | ON              | OFF             | ON              | OFF             | ON    | ON             |

| $+\frac{V_{dc}}{}$  | ON              | ON              | ON              | OFF             | OFF   | OFF            |

| $+\frac{4}{4}$      | ON              | OFF             | OFF             | OFF             | OFF   | OFF            |

|                     | OFF             | OFF             | OFF             | OFF             | OFF   | OFF            |

|                     | ON              | OFF             | OFF             | ON              | OFF   | OFF            |

| 0                   | ON              | ON              | ON              | ON              | OFF   | OFF            |

|                     | OFF             | ON              | ON              | OFF             | OFF   | OFF            |

| $V_{dc}$            | OFF             | OFF             | OFF             | ON              | OFF   | OFF            |

| <u> </u>            | OFF             | ON              | ON              | ON              | OFF   | OFF            |

| $-\frac{V_{dc}}{2}$ | OFF             | ON              | OFF             | ON              | ON    | ON             |

H-bridge inverter, as shown in Table II. The proposed topology is free from neutral-point voltage balancing issues because the clamping diodes are not used unlike in the diode-clamped topologies. The capacitor voltage balancing issues are also eliminated because it does not require any capacitor banks unlike FC inverters. Only a single dc source is used in this configuration; therefore, power balancing issues and issues in regenerating mode are minimized. The magnitude of the dc bus requirement is also less  $(v_{\rm dc}/4)$ . The only additional requirement in this topology is six bidirectional switches with voltage rating of  $v_{\rm dc}/8$ .

#### IV. SPWM

# A. Linear Modulation Region (0 < mi < 1)

Gating pulses for the proposed multilevel inverter are generated using SPWM with a real-time digital simulator. Three modulating signals (sine waves) and four carrier signals

TABLE II

COMPARISON BETWEEN THE CONVENTIONAL TOPOLOGIES

WITH THE PROPOSED TOPOLOGY

|                          | NPC                  | FC                   | H-bridge<br>inverter | Proposed<br>Topology              |

|--------------------------|----------------------|----------------------|----------------------|-----------------------------------|

| Main switches            | 24                   | 24                   | 24                   | 24                                |

| Clamping<br>Diodes       | 36                   | 0                    | 0                    | 0                                 |

| Isolated voltage sources | 1 (V <sub>dc</sub> ) | 1 (V <sub>dc</sub> ) | 6 (V <sub>dc</sub> ) | $1\left(\frac{V_{dc}}{4}\right)$  |

| Capacitors<br>Banks      | 4                    | 18                   | 0                    | 0                                 |

| Bi-directional switches  | 0                    | 0                    | 0                    | $6 \left(\frac{V_{dc}}{8}\right)$ |

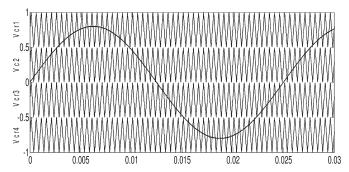

(triangular waves) are used to produce the gating pulses for the proposed topology, as shown in the Fig. 3 [23]. The maximum frequency of the modulating signal (sine wave) is 50 Hz; however, carrier signal frequency is kept constant at 2 kHz. Many switching combinations are possible (which are shown in Table I), but the switching combinations shown in Table III give less switching transitions from one voltage level to another. The remaining switching combinations (in Table I) are used in the case of fault condition, to increase the reliability of the system. In the case of any switch failure of the middle two inverters (inverters 2 and 3), the entire system need not to be shut down. Instead, it can be operated as a three-level inverter up to a modulation index of 0.5 (where modulation index is equal to the ratio of the peak of the modulating signal to four times the peak of the carrier signal, as shown in Fig. 3). For example, when switch  $S_{21}$  is open (or  $S_{22}$  is shorted), the possible switching combinations are shown in Table IV.

Fig. 3. Modulating and carrier waves for generating gating pulses in SPWM.

TABLE III

COMPARISON OF CARRIER AND MODULATING SIGNALS

CORRESPONDING TO THE OUTPUT VOLTAGE

| Comparison between<br>Modulating and<br>Carrier signals | Output<br>Voltage Level | Optimum switching combinations                                          |

|---------------------------------------------------------|-------------------------|-------------------------------------------------------------------------|

| $V_{M} > V_{cr1}$                                       | $+\frac{V_{dc}}{2}$     | $S_{11}$ , $S_{22}$ , $S_{31}$ , $S_{42}$ , $S_1$ and $S_2$             |

| $V_{\rm cr2} < V_{\rm M} < V_{\rm cr1}$                 | $+\frac{V_{dc}}{4}$     | $S_{11}$ , $S_{22}$ , $S_{32}$ and $S_{42}$                             |

| $V_{cr3} < V_M < V_{cr2}$                               | 0                       | S <sub>12</sub> , S <sub>22</sub> , S <sub>32</sub> and S <sub>42</sub> |

| $V_{\rm cr4} < V_{\rm M} < V_{\rm cr3}$                 | $-\frac{V_{dc}}{4}$     | $S_{12},S_{22},S_{32}$ and $S_{41}$                                     |

| $V_{\rm M} < V_{\rm cr4}$                               | $-\frac{V_{dc}}{2}$     | $S_{12}$ , $S_{21}$ , $S_{32}$ , $S_{41}$ , $S_1$ and $S_2$             |

TABLE IV

POSSIBLE SWITCHING COMBINATIONS DURING FAULT CONDITION

| Voltage Magnitude   | S <sub>11</sub> | S <sub>21</sub> | S <sub>31</sub> | S <sub>41</sub> | S <sub>1</sub> | S <sub>2</sub> |

|---------------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|

| $-\frac{V_{dc}}{4}$ | ON              | OFF             | OFF             | OFF             | OFF            | OFF            |

| 0                   | OFF             | OFF             | OFF             | OFF             | OFF            | OFF            |

| $-\frac{V_{dc}}{4}$ | OFF             | OFF             | OFF             | ON              | OFF            | OFF            |

### B. Overmodulation (mi > 1)

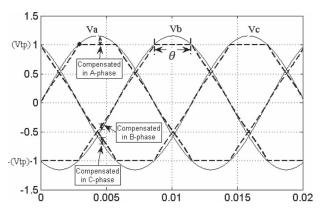

The linear modulation region can be significantly increased by adding the zero-sequence component to the modulating signals in SVPWM [24]. Due to the addition of the zerosequence component, the sum of instantaneous reference phase signals are not equal to zero  $(V_a + V_b + V_c \neq 0)$ , which can produce lower order zero-sequence currents in the motor phase windings. Therefore, the SVPWM technique is not best suitable for those configurations that provide a closed path for zerosequence currents (generally, open-end winding inductionmotor drives with a single dc link) [19]. In this paper, a modified SPWM technique is proposed to operate the configuration in the overmodulation region. In this technique, whenever an A-phase modulating signal is crossing the peak of the upper carrier signal  $V_{\rm tp}$ , it is clamped to  $V_{\rm tp}$ . The subtracted magnitude of the A-phase signal (i.e.,  $V_{\rm a}-V_{\rm tp}$  shown in Fig. 4) is proportionally added to B-phase and C-phase modulating signals such that the sum of the three phase modulating signals equal to zero  $(V_a + V_b + V_c = 0)$ . Hence, the magnitude added to the B-phase is given by  $V_{\rm b}(V_{\rm a}-V_{\rm tp})/V_{\rm a}$ , and that to the C-phase is given by  $V_c(V_a - V_{tp})/V_a$ , as shown in Fig. 4. The same procedure is followed for the B-phase and the C-phase.

It is well known that when the modulation index is varying between 1 to  $2/\sqrt{3}$ , the maximum of one phase modulating

Fig. 4. Three phase modulating waves in overmodulation after compensation.

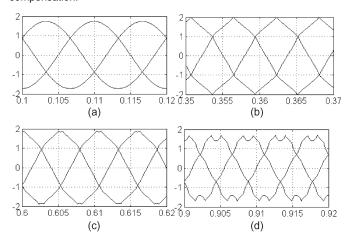

Fig. 5. Three phase line to-line modulating waves in overmodulation after compensation. (a)  $\rm mi=1$ , (b)  $\rm mi=1.15$ , (c)  $\rm mi=1.25$ , and (d)  $\rm mi=1.5$ .

signal crosses the peak of the upper carrier signal, and for a modulation index greater than  $2/\sqrt{3}$ , the maximum of two or three phase modulating signals cross the peak of the carrier signal simultaneously [23]. Therefore, using the proposed method, it is possible to operate the drive in the overmodulation region up to the modulation index of  $2/\sqrt{3}$ . Beyond this modulation index, as two modulating signals are crossing the peak of the carrier wave simultaneously, it results to the considerable reduction in the fundamental component. The line-to-line modulating signals are shown in Fig. 5 for different modulation indexes to demonstrate the maximum possible limit of the modulation index. It is clearly shown in Fig. 5(a) and (b) that the fundamental voltage magnitude is increasing from the modulation index of 1 to  $2/\sqrt{3}$  and it starts decreasing from  $2/\sqrt{3}$ , as shown in Fig. 5(c) and (d).

In the proposed method, the average value of the line-to-line modulating signal is calculated by assuming  $V_{\rm tp}=1$ . The expression for the line-to-line modulating signal is written from Fig. 4 (dotted lines) and integrated from  $\pi/3$  to  $5\pi/6$  (since the waveform is following quarter-wave symmetry, any  $90^\circ$  duration can be considered) to get the average value; this is given in (7), shown at the bottom of the next page, where

$$X1 = V_m \sin\left(\omega t - \frac{2\pi}{3}\right) + V_m \sin\left(\omega t + \frac{2\pi}{3}\right)$$

$$X2 = V_m \sin(\omega t) + V_m \sin\left(\omega t - \frac{2\pi}{3}\right).$$

The expression for the line-to-line modulating signal in conventional SPWM overmodulation is also written from Fig. 4 (solid lines) and integrated from  $\pi/3$  to  $5\pi/6$  as follows:

$$V_{ab}' = \left(\frac{2}{\pi}\right) \begin{bmatrix} \int_{\left(\frac{\pi}{2}\right) - \left(\frac{\theta}{2}\right)}^{\left(\frac{\pi}{2}\right) - \left(\frac{\theta}{2}\right)} \left(V_{m}\sin(\omega t) - V_{m}\sin\left(\omega t - \frac{2\pi}{3}\right)\right) d\omega t \\ + \int_{\left(\frac{\pi}{2}\right) - \left(\frac{\theta}{2}\right)}^{\left(\frac{\pi}{2}\right) + \left(\frac{\theta}{2}\right)} \left(1 - V_{m}\sin\left(\omega t - \frac{2\pi}{3}\right)\right) d\omega t \\ + \int_{\left(\frac{5\pi}{6}\right) - \left(\frac{\theta}{2}\right)}^{\left(\frac{5\pi}{6}\right) - \left(\frac{\theta}{2}\right)} \left(V_{m}\sin(\omega t) - V_{m}\sin\left(\omega t - \frac{2\pi}{3}\right)\right) d\omega t \\ + \int_{\left(\frac{5\pi}{6}\right) - \left(\frac{\theta}{2}\right)}^{\left(\frac{5\pi}{6}\right)} \left(V_{m}\sin(\omega t) - V_{m}\sin\left(\omega t - \frac{2\pi}{3}\right)\right) d\omega t \end{bmatrix}.$$

$$(8)$$

The point to be noticed is that, whenever the peak of the modulating signal is crossing  $V_{\rm tp}$ , it should be clamped to  $V_{\rm tp}$ . Therefore, the reduction in the line-to-line modulating signal of the proposed method when compared with conventional overmodulation is given by

$$V'_{ab} - V_{ab} = \left(\frac{2}{\pi}\right) \left(V_m \sin\left(\frac{\theta}{2}\right) - \left(\frac{\theta}{2}\right) + \sqrt{3} \left[V_m \cos\left(\frac{\theta}{2}\right) - \ln\left(\cos\left(\frac{\theta}{2}\right)\right) - V_m\right]\right)$$

(9)

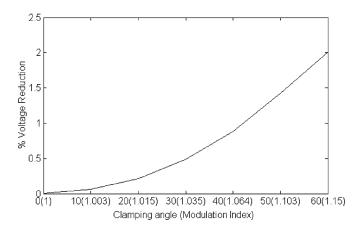

Fig. 6. Percentage magnitude reduction of the line-to-line modulating signal with respect to the modulation index.

where

$$V_m = \frac{1}{\sin\left(\frac{\pi}{2} - \frac{\theta}{2}\right)}.$$

The percentage reduction in the line-to-line modulating signal is calculated, and it is plotted for different

modulation indexes, as shown in Fig. 6. It can be noticed in Fig. 6 that the loss in line-to-line voltage is at the maximum of 2%, which is negligible.

#### V. EXPERIMENTAL RESULTS

The proposed multilevel inverter is experimentally verified with a 5-hp four-pole induction motor. The gating pulses to the proposed multilevel inverter are generated using SPWM

$$V_{ab} = \left(\frac{2}{\pi}\right) \begin{bmatrix} \left(\frac{\pi}{2}\right) - \left(\frac{\theta}{2}\right) \\ \left(\frac{\pi}{3}\right) \end{bmatrix} \left(V_m \sin(\omega t) - V_m \sin\left(\omega t - \frac{2\pi}{3}\right)\right) d\omega t \\ + \int_{\left(\frac{\pi}{2}\right) - \left(\frac{\theta}{2}\right)} \left(1 - \left(V_m \sin\left(\omega t - \frac{2\pi}{3}\right) - \left(\frac{V_m}{X_1}\right) \sin\left(\omega t - \frac{2\pi}{3}\right) \left(V_m \sin(\omega t) - 1\right)\right) d\omega t \\ + \int_{\left(\frac{\pi}{2}\right) - \left(\frac{\theta}{2}\right)} \left(V_m \sin(\omega t) - V_m \sin\left(\omega t - \frac{2\pi}{3}\right)\right) d\omega t \\ + \int_{\left(\frac{\pi}{2}\right) + \left(\frac{\theta}{2}\right)} \left(V_m \sin(\omega t) - V_m \sin\left(\omega t - \frac{2\pi}{3}\right)\right) d\omega t \\ + \int_{\left(\frac{5\pi}{6}\right) - \left(\frac{\theta}{2}\right)} \left(\left[V_m \sin(\omega t) + \left(\frac{V_m}{X_2}\right) \sin(\omega t) \left(V_m \sin\left(\omega t + \frac{2\pi}{3}\right) + 1\right)\right] \\ - \left[V_m \sin\left(\omega t - \frac{2\pi}{3}\right) + \left(\frac{V_m}{X_2}\right) \sin\left(\omega t - \frac{2\pi}{3}\right) \left(V_m \sin\left(\omega t + \frac{2\pi}{3}\right) + 1\right)\right] d\omega t \right)$$

(7)

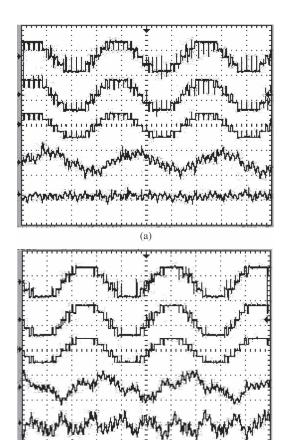

Fig. 7. Top trace is the voltage across the first winding  $(V_{a1}-V_{a2})$ , the second trace is the effective voltage across the total stator phase winding, the third trace is the voltage across the second winding  $(V_{a3}-V_{a4})$ , and the bottom trace is the stator current  $(I_a)$  for the modulation index of (a) 0.4 [y-axis 100 V/div, 2 A/div; x-axis 10 ms/div] and (b) 0.8 [y-axis 100 V/div (for first and third from top), 200 V/div (for second from top), 2 A/div; x-axis 5 ms/div].

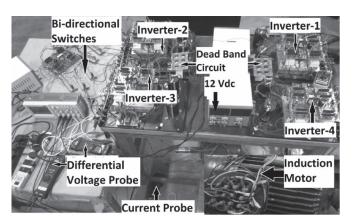

through a real-time digital simulator (eMEGAsim, Opal-RT Technologies). Gating pulses from the real-time digital simulator are given to the deadband circuit that is designed to provide  $2-\mu s$  delay. The output signals of the deadband circuit are given to the gate driver circuits.

Fig. 7(a) shows the experimental results for the modulation index of 0.4. It is clear from the results shown in Fig. 7(a) that voltage across the motor phase winding is the sum of the voltage across the individual windings, and the voltage profile is similar to a three-level operation up to the modulation index of 0.5. The experimental result for the modulation index of 0.8 is shown in Fig. 7(b). If the modulation index greater than 0.5, the reference wave passes through all four carrier signals, producing multilevel voltage waveform across the motor terminals.

It can be observed in Fig. 8(a) that only inverters 1 and 4 are switching and inverters 2 and 3 are clamped. In the case of conventional (NPC or FC) multilevel inverters, all the switches are required to be switched for balancing the capacitor voltage, which results in more switching losses. However, in the proposed topology, it is noticed in Fig. 8(a) that the middle two inverters are not switching; therefore, in the region of the modulation index less than 0.5, the switching losses are reduced. It can be noticed in Fig. 8(b) that, the middle two

Fig. 8. Top trace is the inverter-1 pole voltage, the second trace is the inverter-4 pole voltage, the third trace is the voltage between the middle two inverters, and the bottom trace is the voltage across bidirectional switch for the modulation index of (a) 0.4 [y-axis 100 V/div; x-axis 25 ms/div] and (b) 0.8 [y-axis 100 V/div; x-axis 5 ms/div].

inverters are switched to provide the voltage levels of  $+(v_{\rm dc}/2)$  and  $-(v_{\rm dc}/2)$  for the modulation index greater than 0.5. It can also be noticed that the maximum voltage appearing across the bidirectional switch is  $v_{\rm dc}/8$  only.

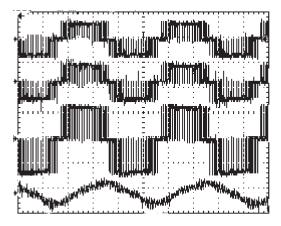

The results for the modulation index of  $2/\sqrt{3}$  are shown in Fig. 9(a), which demonstrate the validity of the proposed configuration in the overmodulation region using the modified SPWM technique. It is clearly shown in Fig. 9(a) that zero-sequence currents flowing through motor phase windings are close to zero. Results for the same modulation index with a conventional SPWM technique are presented in Fig. 9(b) to show the significance of the proposed PWM technique. It is evident in Fig. 9(a) and (b) that zero-sequence currents are significantly low in the proposed PWM technique.

In the case of any switch failure of inverter 2 or 3, the proposed topology need not be shut down; instead, it can be operated as a three-level inverter up to the modulation index of 0.5, as shown in Fig. 10, thereby increasing the reliability of the system when compared with conventional five-level (NPC or FC) inverters. The experimental setup is shown in Fig. 11.

It is evident from all the above results that the proposed topology can be operated in the complete linear modulation region using SPWM and in the overmodulation region up to the modulation index of  $2/\sqrt{3}$  using the modified SPWM technique with a single DC link.

Fig. 9. Top trace is the voltage across the first winding  $(V_{\rm a1}-V_{\rm a2})$ , the second trace is the effective voltage across the total stator phase winding, the third trace is the voltage across the second winding  $(V_{\rm a3}-V_{\rm a4})$ , the fourth trace is the stator current  $(I_{\rm a})$ , and bottom trace is the zero-sequence currents for the modulation index of  $2/\sqrt{3}$ . (a) Proposed method [y-axis (200 V/div, 500 V/div, 2 A/div, x-axis 5 ms/div]. (b) Conventional SPWM [y-axis (200 V/div, 500 V/div, 2 A/div, x-axis 5 ms/div].

(b)

Fig. 10. Top trace is the voltage across the first winding  $(V_{a1}-V_{a2})$ , the second trace is the voltage across the second winding  $(V_{a3}-V_{a4})$ , the third trace is the effective voltage across the total stator phase winding, and the bottom trace is the stator current  $(I_a)$  for the modulation index of 0.5 during fault condition [y-axis 100 V/div, 2 A/div, x-axis 10 ms/div].

### VI. CONCLUSION

In this paper, a multilevel inverter topology has been presented for a four-pole induction-motor drive. The disconnected

Fig. 11. Experimental setup.

two IVPWCs are fed from four two-level inverters. All these four two-level inverters are connected to a single dc source minimizing the power balancing issues. The magnitude of dc source voltage requirement is also very less compared with that of conventional five-level inverter topologies. This topology uses only two-level inverters; hence, it is free from capacitor voltage balancing issues. The proposed topology is experimentally verified with a 5-hp four-pole induction motor using a laboratory prototype. Gating pulses are generated using the SPWM technique for the linear modulation region and for the overmodulation region using the modified SPWM technique. In the case of any switch failure of the middle two inverters, the topology can be operated as a three-level inverter up to the modulation index of 0.5. This will increase the reliability of the system during fault condition when compared with conventional NPC or FC topologies. This topology does not require any major design modifications of the induction motor except the disconnection of IVPWCs. This concept can also be applied to obtain a higher number of voltage levels for the induction motor with a higher number of poles, which requires more two-level inverters.

#### REFERENCES

- J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multi-level voltage-source-converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [2] J. Ewanchuk and J. Salmon, "Three-limb coupled inductor operation for paralleled multi-level three-phase voltage sourced inverters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1979–1988, May 2013.

- [3] M. Hamzeh, A. Ghazanfari, H. Mokhtari, and H. Karimi, "Integrating hybrid power source into an islanded mv microgrid using CHB multilevel inverter under unbalanced and nonlinear load conditions," *IEEE Trans. Energy Convers.*, vol. 28, no. 3, pp. 643–651, Sep. 2013.

- [4] M. M. Renge and H. M. Suryawanshi, "Five-level diode clamped inverter to eliminate common mode voltage and reduced dv/dt in medium voltage rating induction motor drives," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1598–1607, Jul. 2008.

- [5] B. A. Welchko, T. A. Lipo, T. M. Jahns, and S. E. Schulz, "Fault tolerant three-phase AC motor drive topologies: A comparison of features, cost, limitations," *IEEE Trans. Power Electron.*, vol. 19, no. 4, pp. 1108–1116, Jul. 2004.

- [6] M. A. Parker, L. Ran, and S. J. Finney, "Distributed control of a fault-tolerant modular multilevel inverter for direct-drive wind turbine grid interfacing," *IEEE Trans. Ind. Electron.*, vol. 60, no. 2, pp. 509–522, Feb. 2013.

- [7] T. Boller, J. Holtz, and A. K. Rathore, "Neutral-point potential balancing using synchronous optimal pulsewidth modulation of multilevel inverters in medium-voltage high-power AC drives," *IEEE Trans. Ind. Appl.*, vol. 50, no. 1, pp. 549–557, Jan./Feb. 2014.

- [8] M. Khazraei, H. Sepahvand, K. A. Corzine, and M. Ferdowsi, "Active capacitor voltage balancing in single-phase flying-capacitor multilevel power converters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 769– 778, Feb. 2012.

- [9] R. Maheshwari, S. Munk-Nielsen, and S. Busquets-Monge, "Design of neutral-point voltage controller of a three-level NPC inverter with small DC-link capacitors," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1861– 1871, May 2013.

- [10] F. Carnielutti, H. Pinheiro, and C. Rech, "Generalized carrier-based modulation strategy for cascaded multilevel converters operating under fault conditions," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 679–689, Feb. 2012.

- [11] B. Diong, H. Sepahvand, and K. A. Corzine, "Harmonic distortion optimization of cascaded H-bridge inverters considering device voltage drops and noninteger DC voltage ratios," *IEEE Trans. Ind. Electron.*, vol. 60, no. 8, pp. 3106–3114, Aug. 2013.

- [12] V. T. Somasekhar, K. Gopakumar, M. R. Baiju, K. K. Mohapatra, and L. Umanand, "A multilevel inverter system for an induction motor with open-end windings," *IEEE Trans. Ind. Electron.*, vol. 52, no. 3, pp. 824– 836. Jun. 2005.

- [13] J. Ewanchuk, J. Salmon, and C. znd Chapelsky, "A method for supply voltage boosting in an open-ended induction machine using a dual inverter system with a floating capacitor bridge," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1348–1357, Mar. 2013.

- [14] G. Mondal, K. Gopakumar, N. Tekwani, and E. Levi, "A reduced-switch-count five-level inverter with common-mode voltage elimination for an open-end winding induction motor drive," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2344–2351, Aug. 2007.

- [15] K. Sivakumar, A. Das, R. Ramchand, C. Patel, and K. Gopakumar, "A five-level inverter scheme for a four-pole induction motor drive by feeding the identical voltage-profile windings from both sides," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2776–2784, Aug. 2010.

- [16] E. Cengelci, P. N. Enjeti, and J. W. Gray, "A new modular motor-modular inverter concept for medium-voltage adjustable-speed-drive systems," *IEEE Trans. Ind. Appl.*, vol. 36, no. 3, pp. 786–796, May/Jun. 2000.

- [17] K. K. Nallmekala and K. Sivakumar, "A five-level inverter topology for four pole induction motor drive with single DC link," in *Proc. EEEIC*, May 2012, pp. 84–89.

- [18] M. R. Baiju, K. K. Mohapatra, R. S. Kanchan, and K. Gopakumar, "A dual two-level inverter scheme with common mode voltage elimination for an induction motor drive," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 794–805, May 2004.

- [19] V. T. Somasekhar, S. Srinivas, B. Prakash Reddy, C. Nagarjuna Reddy, and K. Sivakumar, "Pulse width-modulated switching strategy for the dynamic balancing of zero-sequence current for a dual-inverter fed openend winding induction motor drive," *IET Elect. Power Appl.*, vol. 1, no. 4, pp. 591–600, Jul. 2007.

- [20] N. Bodo, E. Levi, and M. Jones, "Investigation of carrier-based PWM techniques for a five-phase open-end winding drive topology," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 2054–2065, May 2013.

- [21] A. L. Batschauer, S. A. Mussa, and M. L. Heldwein, "Three-phase hybrid multilevel inverter based on half-bridge modules," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 668–678, Feb. 2012.

- [22] P. C. Kruase, O. Wasynczuk, and S. D. Sudhoff, "Basic principles for electric machine analysis," in *Analysis of Electrical Machinery and Drive Systems*, 2nd ed. Piscataway, NJ, USA: IEEE Press, 2002.

- [23] M. K. Modi, S. Venugopal, and G. Narayanan, "Space vector based analysis of overmodulation in triangle-comparison based PWM for voltage source inverter," *Sadhana*, vol. 38, pt. 3, pp. 331–358, Jun. 2013.

- [24] A. Dey, P. P. Rajeevan, R. Ramchand, K. Mathew, and K. Gopakumar, "A space-vector-based hysteresis current controller for a general n-level inverter-fed drive with nearly constant switching frequency control," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1989–1998, May 2013.

- [25] A. Somani, R. K. Gupta, K. K. Mohapatra, and N. Mohan, "On the causes of circulating currents in PWM drives with open-end winding AC machines," *IEEE Trans. Ind. Electron.*, vol. 60, no. 9, pp. 3670–3678, Sep. 2013.

ac drives.

Kiran Kumar N. received the B.Tech. degree in electrical and electronics engineering from Gudlavalleru Engineering College, Gudlavalleru, India, in 2006 and the M.Tech. degree in power control and drives from the National Institute of Technology, Rourkela, India, in 2008. He is currently working toward the Ph.D. degree at the Indian Institute of Technology Hyderabad, Hyderabad, India.

His research interests include multilevel inverters, pulsewidth modulation techniques, and

K. Sivakumar (M'12) received the B.Tech. degree in electrical engineering from Sri Venkateswara University, Tirupati, India, in 2004, the M.Tech. degree in power electronics from the National Institute of Technology, Warangal, India, in 2006, and the Ph.D. degree from the Indian Institute of Science, Bangalore, India, in 2010.

He is currently an Assistant Professor with the Department of Electrical Engineering, Indian Institute of Technology Hyderabad, Hyderabad,

India. His research interests include multilevel inverters, open-end winding induction-motor drives, pulsewidth modulation techniques, switched-mode power conversion, microgrids, and power quality and control.