# Data Encoding Techniques for Reducing Energy Consumption in Network-on-Chip

Nima Jafarzadeh, Maurizio Palesi, *Member, IEEE*, Ahmad Khademzadeh, and Ali Afzali-Kusha, *Senior Member, IEEE*

Abstract—As technology shrinks, the power dissipated by the links of a network-on-chip (NoC) starts to compete with the power dissipated by the other elements of the communication subsystem, namely, the routers and the network interfaces (NIs). In this paper, we present a set of data encoding schemes aimed at reducing the power dissipated by the links of an NoC. The proposed schemes are general and transparent with respect to the underlying NoC fabric (i.e., their application does not require any modification of the routers and link architecture). Experiments carried out on both synthetic and real traffic scenarios show the effectiveness of the proposed schemes, which allow to save up to 51% of power dissipation and 14% of energy consumption without any significant performance degradation and with less than 15% area overhead in the NI.

Index Terms—Coupling switching activity, data encoding, interconnection on chip, low power, network-on-chip (NoC), power analysis.

### I. INTRODUCTION

HIFTING from a silicon technology node to the next one results in faster and more power efficient gates but slower and more power hungry wires [1]. In fact, more than 50% of the total dynamic power is dissipated in interconnects in current processors, and this is expected to rise to 65%–80% over the next several years [2]. Global interconnect length does not scale with smaller transistors and local wires. Chip size remains relatively constant because the chip function continues to increase and RC delay increases exponentially. At 32/28 nm, for instance, the RC delay in a 1-mm global wire at the minimum pitch is  $25\times$  higher than the intrinsic delay of a two-input NAND fanout of 5 [1].

If the raw computation horsepower seems to be unlimited, thanks to the ability of instancing more and more cores in a single silicon die, scalability issues, due to the need of making efficient and reliable communication between the increasing

Manuscript received July 16, 2012; revised February 2, 2013; accepted February 5, 2013. Date of publication March 28, 2013; date of current version February 20, 2014.

N. Jafarzadeh is with the Department of Computer Science, Science and Research Branch, Islamic Azad University, Tehran 14515-775, Iran (e-mail: n.zadeh@ieee.org).

M. Palesi is with the Kore University of Enna, Enna 94100, Italy (e-mail: maurizio.palesi@unikore.it).

A. Khademzadeh is with the Iran Telecommunication Research Center, Tehran 16846-13114, Iran (e-mail: zadeh@itrc.ac).

A. Afzali-Kusha is with the School of Electrical and Computer Engineering, College of Engineering, University of Tehran, Tehran 14395, Iran (e-mail: afzali@ut.ac.ir).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2013.2251020

number of cores, become the real problem [3]. The network-on-chip (NoC) design paradigm [4] is recognized as the most viable way to tackle with scalability and variability issues that characterize the ultradeep submicronmeter era.

Nowadays, the on-chip communication issues are as relevant as, and in some cases more relevant than, the computation-related issues [4]. In fact, the communication subsystem increasingly impacts the traditional design objectives, including cost (i.e., silicon area), performance, power dissipation, energy consumption, reliability, etc. As technology shrinks, an ever more significant fraction of the total power budget of a complex many-core system-on-chip (SoC) is due to the communication subsystem.

In this paper, we focus on techniques aimed at reducing the power dissipated by the network links. In fact, the power dissipated by the network links is as relevant as that dissipated by routers and network interfaces (NIs) and their contribution is expected to increase as technology scales [5]. In particular, we present a set of data encoding schemes operating at flit level and on an end-to-end basis, which allows us to minimize both the switching activity and the coupling switching activity on links of the routing paths traversed by the packets. The proposed encoding schemes, which are transparent with respect to the router implementation, are presented and discussed at both the algorithmic level and the architectural level, and assessed by means of simulation on synthetic and real traffic scenarios. The analysis takes into account several aspects and metrics of the design, including silicon area, power dissipation, and energy consumption. The results show that by using the proposed encoding schemes up to 51% of power and up to 14% of energy can be saved without any significant degradation in performance and with 15% area overhead in the NI.

The rest of this paper is organized as follows. We briefly discuss related works in Section II, while Section III presents an overview of the proposed data encoding schemes. The proposed data encoding schemes along with possible hardware implementations and their analysis are described in Section IV. In Section V, the results for the hardware overhead, power and energy savings, and performance reduction of the proposed data encoding schemes are compared with those of other approaches. Finally, this paper is concluded in Section VI.

### II. RELATED WORKS AND CONTRIBUTIONS

In the next several years, the availability of chips with 1000 cores is foreseen [6]. In these chips, a significant fraction of

the total system power budget is dissipated by interconnection networks. Therefore, the design of power-efficient interconnection networks has been the focus of many works published in the literature dealing with NoC architectures. These works concentrate on different components of the interconnection networks such as routers, NIs, and links. Since the focus of this paper is on reducing the power dissipated by the links, in this section, we briefly review some of the works in the area of link power reduction. These include the techniques that make use of shielding [7], [8], increasing line-to-line spacing [9], [10], and repeater insertion [11]. They all increase the chip area. The data encoding scheme is another method that was employed to reduce the link power dissipation. The data encoding techniques may be classified into two categories. In the first category, encoding techniques concentrate on lowering the power due to self-switching activity of individual bus lines while ignoring the power dissipation owing to their coupling switching activity. In this category, bus invert (BI) [12] and INC-XOR [13] have been proposed for the case that random data patterns are transmitted via these lines. On the other hand, gray code [14], T0 [15], working-zone encoding [16], and T0-XOR [17] were suggested for the case of correlated data patterns. Application-specific approaches have also been proposed [18]–[22].

This category of encoding is not suitable to be applied in the deep submicronmeter technology nodes where the coupling capacitance constitutes a major part of the total interconnect capacitance. This causes the power consumption due to the coupling switching activity to become a large fraction of the total link power consumption, making the aforementioned techniques, which ignore such contributions, inefficient [23]. The works in the second category concentrate on reducing power dissipation through the reduction of the coupling switching [10], [22]-[30]. Among these schemes [10], [24]–[28], the switching activity is reduced using many extra control lines. For example, the data bus width grows from 32 to 55 in [24]. The techniques proposed in [29] and [30] have a smaller number of control lines but the complexity of their decoding logic is high. The technique described in [29] is as follows: first, the data are both odd inverted and even inverted, and then transmission is performed using the kind of inversion which reduces more the switching activity. In [30], the coupling switching activity is reduced up to 39%. In this paper, compared to [30], we use a simpler decoder while achieving a higher activity reduction.

Let us now discuss in more detail the works with which we compare our proposed schemes. In [12], the number of transitions from 0 to 1 for two consecutive flits (the flit that just traversed and the one which is about to traverse the link) is counted. If the number is larger than half of the link width, the inversion will be performed to reduce the number of 0 to 1 transitions when the flit is transferred via the link. This technique is only concerned about the self-switching without worrying the coupling switching. Note that the coupling capacitance in the state-of-the-art silicon technology is considerably larger (e.g., four times) compared with the self-capacitance, and hence, should be considered in any scheme proposed for the link power reduction.

$\label{eq:table_interpolation} \textbf{TABLE I}$  Effect of Odd Inversion on Change of Transition Types

| Time  | Normal         |                |        | Odd Inverted          |                |         |  |

|-------|----------------|----------------|--------|-----------------------|----------------|---------|--|

|       | Type I         |                |        | Types II, III, and IV |                |         |  |

| t - 1 | 00, 11         | 00, 11, 01, 10 | 01, 10 | 00, 11                | 00, 11, 01, 10 | 01, 10  |  |

| t     | 10, 01         | 01, 10, 00, 11 | 11, 00 | 11, 00                | 00, 11, 01, 10 | 10, 01  |  |

|       | T1*            | T1**           | T1***  | Type III              | Type IV        | Type II |  |

| t - 1 | Type II        |                |        | Type I                |                |         |  |

|       | 01, 10         |                |        | 01, 10                |                |         |  |

| t     |                | 10, 01         |        | 11, 00                |                |         |  |

| t - 1 | Type III       |                |        | Type I                |                |         |  |

|       | 00, 11         |                |        | 00, 11                |                |         |  |

| t     | 11, 00         |                |        | 10, 01                |                |         |  |

| t - 1 | Type IV        |                |        | Type I                |                |         |  |

|       | 00, 11, 01, 10 |                |        | 00, 11, 01, 10        |                |         |  |

| t     | 00, 11, 01, 10 |                |        | 01, 10, 00, 11        |                |         |  |

In addition, the scheme was based on the hop-by-hop technique, and therefore, encoding/decoding is performed in each node.

The scheme presented in [26] dealt with reducing the coupling switching. In this method, a complex encoder counts the number of Type I (Table I) transitions with a weighting coefficient of one and the number of Type II transitions with the weighting coefficient of two. If the number is larger than half of the link width, the inversion will be performed. In addition to the complex encoder, the technique only works on the patterns whose full inversion leads to the link power reduction while not considering the patterns whose full inversions may lead to higher link power consumption. Therefore, the link power reduction achieved through this technique is not as large as it could be. This scheme was also based on the hop-by-hop technique.

In another coding technique presented in [25], bunches of four bits are encoded with five bits. The encoded bits were isolated using shielding wires such that the occurrence of the patterns "101" and "010" were prevented. This way, no simultaneous Type II transitions in two adjacent pair bits are induced. This technique effectively reduces the coupling switching activity. Although the technique reduces the power consumption considerably, it increases the data transfer time, and, hence, the link energy consumption. This is due to the fact that for each four bits, six bits are transmitted which increases the communication traffic. This technique was also based on the hop-by-hop approach.

A coding technique that reduces the coupling switching activity by taking the advantage of end-to-end encoding for wormhole switching has been presented in [23]. It is based on lowering the coupling switching activity by eliminating only Type II transitions.

In this paper, we present three encoding schemes. In Scheme I, we focus on reducing Type I transitions while in Scheme II, both Types I and II transitions are taken into account for deciding between half and full invert, depending the amount of switching reduction. Finally, in Scheme III, we consider the fact that Type I transitions show different behaviors in the case of odd and even inverts and make the inversion which leads to the higher power saving.

#### III. OVERVIEW OF THE PROPOSAL

The basic idea of the proposed approach is encoding the flits before they are injected into the network with the goal of minimizing the self-switching activity and the coupling switching activity in the links traversed by the flits. In fact, self-switching activity and coupling switching activity are responsible for link power dissipation. In this paper, we refer to the end-to-end scheme. This end-to-end encoding technique takes advantage of the pipeline nature of the wormhole switching technique [4]. Note that since the same sequence of flits passes through all the links of the routing path, the encoding decision taken at the NI may provide the same power saving for all the links. For the proposed scheme, an encoder and a decoder block are added to the NI. Except for the header flit, the encoder encodes the outgoing flits of the packet such that the power dissipated by the inter-router point-to-point link is minimized [23].

#### IV. PROPOSED ENCODING SCHEMES

In this section, we present the proposed encoding scheme whose goal is to reduce power dissipation by minimizing the coupling transition activities on the links of the interconnection network. Let us first describe the power model that contains different components of power dissipation of a link. The dynamic power dissipated by the interconnects and drivers is

$$P = [T_{0\to 1} (C_s + C_l) + T_c C_c] V_{dd}^2 F_{ck}$$

(1)

where  $T_{0 \to 1}$  is the number of  $0 \to 1$  transitions in the bus in two consecutive transmissions,  $T_c$  is the number of correlated switching between physically adjacent lines,  $C_s$  is the line to substrate capacitance,  $C_l$  is the load capacitance,  $C_c$  is the coupling capacitance,  $V_{\rm dd}$  is the supply voltage, and  $F_{\rm ck}$  is the clock frequency. One can classify four types of coupling transitions as described in [26]. A Type I transition occurs when one of the lines switches when the other remains unchanged. In a Type II transition, one line switches from low to high while the other makes transition from high to low. A Type III transition corresponds to the case where both lines switch simultaneously. Finally, in a Type IV transition both lines do not change.

The effective switched capacitance varies from type to type, and hence, the coupling transition activity,  $T_c$ , is a weighted sum of different types of coupling transition contributions [26]. Therefore

$$T_c = K_1 T_1 + K_2 T_2 + K_3 T_3 + K_4 T_4 \tag{2}$$

where  $T_i$  is the average number of Type i transition and  $K_i$  is its corresponding weight. According to [26], we use  $K_1 = 1$ ,  $K_2 = 2$ , and  $K_3 = K_4 = 0$ . The occurrence probability of Types I and II for a random set of data is 1/2 and 1/8, respectively. This leads to a higher value for  $K_1T_1$  compared with  $K_2T_2$  suggesting that minimizing the number of Type I transition may lead to a considerable power reduction. Using (2), one may express (1) as

$$P = [T_{0\to 1} (C_s + C_l) + (T_1 + 2T_2) C_c] V_{dd}^2 F_{ck}.$$

(3)

According to [3],  $C_l$  can be neglected

$$P \propto T_{0 \to 1} C_s + (T_1 + 2T_2) C_c.$$

(4)

Here, we calculate the occurrence probability for different types of transitions. Consider that flit (t-1) and flit (t) refer to the previous flit which was transferred via the link and the flit which is about to pass through the link, respectively. We consider only two adjacent bits of the physical channel. Sixteen different combinations of these four bits could occur (Table I). Note that the first bit is the value of the generic ith line of the link, whereas the second bit represents the value of its (i + 1)th line. The number of transitions for Types I, II, III, and IV are 8, 2, 2, and 4, respectively. For a random set of data, each of these sixteen transitions has the same probability. Therefore, the occurrence probability for Types I, II, III, and IV are 1/2, 1/8, 1/8, and 1/4, respectively. In the rest of this section, we present three data encoding schemes designed for reducing the dynamic power dissipation of the network links along with a possible hardware implementation of the decoder.

#### A. Scheme I

In scheme I, we focus on reducing the numbers of Type I transitions (by converting them to Types III and IV transitions) and Type II transitions (by converting them to Type I transition). The scheme compares the current data with the previous one to decide whether odd inversion or no inversion of the current data can lead to the link power reduction.

1) Power Model: If the flit is odd inverted before being transmitted, the dynamic power on the link is

$$P' \propto T'_{0 \to 1} + (K_1 T'_1 + K_2 T'_2 + K_3 T'_3 + K_4 T'_4) C_c$$

(5)

where  $T'_{0\rightarrow 1}$ ,  $T'_1$ ,  $T'_2$ ,  $T'_3$ , and  $T'_4$ , are the self-transition activity, and the coupling transition activity of Types I, II, III, and IV, respectively. Table I reports, for each transition, the relationship between the coupling transition activities of the flit when transmitted as is and when its bits are odd inverted. Data are organized as follows. The first bit is the value of the generic *i*th line of the link, whereas the second bit represents the value of its (i+1)th line. For each partition, the first (second) line represents the values at time t-1 (t).

As Table I shows, if the flit is odd inverted, Types II, III, and IV transitions convert to Type I transitions. In the case of Type I transitions, the inversion leads to one of Types II, III, or Type IV transitions. In particular, the transitions indicated as  $T_1^*$ ,  $T_1^{**}$ , and  $T_1^{***}$  in the table convert to Types II, III, and IV transitions, respectively. Also, we have  $T'_{0\rightarrow 1} = T_{0\rightarrow 0(\text{odd})} + T_{0\rightarrow 1(\text{even})}$  where odd/even refers to odd/even lines. Therefore, (5) can be expressed as

$$P \propto (T_{0 \to 0(\text{odd})} + T_{0 \to 1(\text{even})}) C_s + [K_1 (T_2 + T_3 + T_4) + K_2 T_1^{***} + K_3 T_1^* + K_4 T_1^{**}] C_c.$$

(6)

Thus, if P > P', it is convenient to odd invert the flit before transmission to reduce the link power dissipation. Using (4) and (6) and noting that  $C_c/C_s = 4$  [26], we obtain the following odd invert condition

$$\frac{1}{4}T_{0\to 1} + T_1 + 2T_2 > \frac{1}{4} \left( T_{0\to 0(\text{odd})} + T_{0\to 1(\text{even})} \right) + T_2 + T_3 + T_4 + 2T_1^{***}.$$

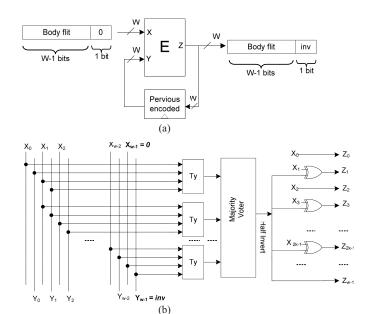

Fig. 1. Encoder architecture scheme I. (a) Circuit diagram [27]. (b) Internal view of the encoder block (E).

Also, since  $T_{0\rightarrow 1} = T_{0\rightarrow 1(\text{odd})} + T_{0\rightarrow 1(\text{even})}$ , one may write

$$\frac{1}{4}T_{0\to 1(\text{odd})} + T_1 + 2T_2 > \frac{1}{4}T_{0\to 0(\text{odd})} + T_2 + T_3 + T_4 + 2T_1^{***}$$

(7)

which is the exact condition to be used to decide whether the odd invert has to be performed. Since the terms  $T_{0 \to 1(\text{odd})}$  and  $T_{0 \to 0(\text{odd})}$  are weighted with a factor of 1/4, for link widths greater than 16 bits, the misprediction of the invert condition will not exceed 1.2% on average [23]. Thus, we can approximate the exact condition as

$$T_1 + 2T_2 > T_2 + T_3 + T_4 + 2T_1^{***}.$$

(8)

Of course, the use of the approximated odd invert condition reduces the effectiveness of the encoding scheme due to the error induced by the approximation but it simplifies the hardware implementation of encoder. Now, defining

$$T_x = T_3 + T_4 + T_1^{***}$$

and

$$T_{v} = T_2 + T_1 - T_1^{***} \tag{9}$$

one can rewrite (8) as

$$T_{\rm v} > T_{\rm r}. \tag{10}$$

Assuming the link width of w bits, the total transition between adjacent lines is w-1, and hence

$$T_y + T_x = w - 1. (11)$$

Thus, we can write (10) as

$$T_{y} > \frac{(w-1)}{2}.$$

(12)

This presents the condition used to determine whether the odd inversion has to be performed or not.

2) Proposed Encoding Architecture: The proposed encoding architecture, which is based on the odd invert condition defined by (12), is shown in Fig. 1. We consider a link width of w bits. If no encoding is used, the body flits are grouped in w bits by the NI and are transmitted via the link. In our approach, one bit of the link is used for the inversion bit, which indicates if the flit traversing the link has been inverted or not. More specifically, the NI packs the body flits in w-1 bits [Fig. 1(a)]. The encoding logic E, which is integrated into the NI, is responsible for deciding if the inversion should take place and performing the inversion if needed. The generic block diagram shown in Fig. 1(a) is the same for all three encoding schemes proposed in this paper and only the block E is different for the schemes. To make the decision, the previously encoded flit is compared with the current flit being transmitted. This latter, whose w bits are the concatenation of w-1 payload bits and a "0" bit, represents the first input of the encoder, while the previous encoded flit represents the second input of the encoder [Fig. 1(b)]. The w-1 bits of the incoming (previous encoded) body flit are indicated by  $X_i$   $(Y_i)$ , i = 0, 1, ..., w - 2. The wth bit of the previously encoded body flit is indicated by inv which shows if it was inverted (inv = 1) or left as it was (inv = 0). In the encoding logic, each  $T_v$  block takes the two adjacent bits of the input flits (e.g.,  $X_1X_2Y_1Y_2$ ,  $X_2X_3Y_2Y_3$ ,  $X_3X_4Y_3Y_4$ , etc.) and sets its output to "1" if any of the transition types of  $T_{\nu}$  is detected. This means that the odd inverting for this pair of bits leads to the reduction of the link power dissipation (Table I). The  $T_{\nu}$  block may be implemented using a simple circuit. The second stage of the encoder, which is a majority voter block, determines if the condition given in (12) is satisfied (a higher number of 1s in the input of the block compared to 0s). If this condition is satisfied, in the last stage, the inversion is performed on odd bits. The decoder circuit simply inverts the received flit when the inversion bit is high.

#### B. Scheme II

In the proposed encoding scheme II, we make use of both odd (as discussed previously) and full inversion. The full inversion operation converts Type II transitions to Type IV transitions. The scheme compares the current data with the previous one to decide whether the odd, full, or no inversion of the current data can give rise to the link power reduction.

1) Power Model: Let us indicate with P, P', and P'' the power dissipated by the link when the flit is transmitted with no inversion, odd inversion, and full inversion, respectively. The odd inversion leads to power reduction when P' < P'' and P' < P. The power P'' is given by [23]

$$P'' \propto T_1 + 2T_4^{**}. \tag{13}$$

Neglecting the self-switching activity, we obtain the condition P' < P'' as [see (7) and (13)]

$$T_2 + T_3 + T_4 + 2T_1^{***} < T_1 + 2T_4^{**}.$$

(14)

Therefore, using (9) and (11), we can write

$$2(T_2 - T_4^{**}) < 2T_y - w + 1. (15)$$

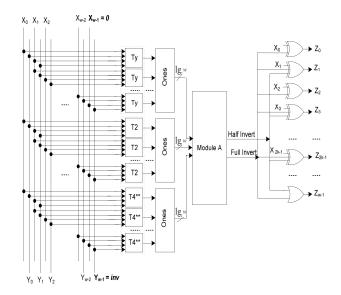

Fig. 2. Encoder architecture Scheme II.

Based on (12) and (15), the odd inversion condition is obtained as

$$2\left(T_2 - T_4^{**}\right) < 2T_y - w + 1 \quad T_y > \frac{(w-1)}{2}.\tag{16}$$

Similarly, the condition for the full inversion is obtained from P'' < P and P'' < P'. The inequality P'' < P is satisfied when [23]

$$T_2 > T_4^{**}.$$

(17)

Therefore, using (15) and (17), the full inversion condition is obtained as

$$2(T_2 - T_4^{**}) > 2T_v - w + 1 \quad T_2 > T_4^{**}.$$

(18)

When none of (16) or (18) is satisfied, no inversion will be performed.

2) Proposed Encoding Architecture: The operating principles of this encoder are similar to those of the encoder implementing Scheme I. The proposed encoding architecture, which is based on the odd invert condition of (16) and the full invert condition of (18), is shown in Fig. 2. Here again, the wth bit of the previously and the full invert condition of (18) is shown in Fig. 2. Here again, the wth bit of the previously encoded body flit is indicated with inv which defines if it was odd or full inverted (inv = 1) or left as it was (inv = 0). In this encoder, in addition to the  $T_y$  block in the Scheme I encoder, we have the  $T_2$  and  $T_4^{**}$  blocks which determine if the inversion based on the transition types  $T_2$  and  $T_4^{**}$  should be taken place for the link power reduction. The second stage is formed by a set of 1s blocks which count the number of 1s in their inputs. The output of these blocks has the width of  $\log_2 w$ . The output of the top 1s block determines the number of transitions that odd inverting of pair bits leads to the link power reduction. The middle 1s block identifies the number of transitions whose full inverting of pair bits leads to the link power reduction. Finally, the bottom 1s block specifies the number of transitions whose full inverting of pair bits leads to the increased link power. Based on the number of 1s for each transition type, Module A decides if an odd invert or full invert action should be performed for the power reduction.

Fig. 3. Decoder architecture Scheme II. (a) Circuit diagram. (b) Internal view of the decoder block (D).

For this module, if (16) or (18) is satisfied, the corresponding output signal will become "1." In case no invert action should be taken place, none of the output is set to "1." Module A can be implemented using full-adder and comparator blocks. The circuit diagram of the decoder is shown in Fig. 3. The w bits of the incoming (previous) body flit are indicated by  $Z_i$   $(R_i)$ , i = 0, 1, ..., w - 1. The wth bit of the body flit is indicated by inv which shows if it was inverted (inv = 1) or left as it was (inv = 0). For the decoder, we only need to have the  $T_y$  block to determine which action has been taken place in the encoder. Based on the outputs of these blocks, the majority voter block checks the validity of the inequality given by (12). If the output is "0" ("1") and the inv = 1, it means that half (full) inversion of the bits has been performed. Using this output and the logical gates, the inversion action is determined. If two inversion bits were used, the overhead of the decoder hardware could be substantially reduced.

### C. Scheme III

In the proposed encoding Scheme III, we add even inversion to Scheme II. The reason is that odd inversion converts some of Type I  $(T_1^{****})$  transitions to Type II transitions. As can be observed from Table II, if the flit is even inverted, the transitions indicated as  $T_1^{***}/T_1^{****}$  in the table are converted to Type IV/Type III transitions. Therefore, the even inversion may reduce the link power dissipation as well. The scheme compares the current data with the previous one to decide whether odd, even, full, or no inversion of the current data can give rise to the link power reduction.

1) Power Model: Let us indicate with P', P'', and  $P^{'''}$  the power dissipated by the link when the flit is transmitted with no inversion, odd inversion, full inversion, and even inversion, respectively. Similar to the analysis given for Scheme I, we can approximate the condition  $P^{'''} < P$  as

$$T_1 + 2T_2 > T_2 + T_3 + T_4 + 2T_1^*$$

(19)

$\label{thm:table II} \textbf{Effect of Even Inversion on Change of Transition Types}$

| Time  | Normal         |                |        | Even Inverted         |                |          |  |

|-------|----------------|----------------|--------|-----------------------|----------------|----------|--|

|       | Type I         |                |        | Types II, III, and IV |                |          |  |

| t - 1 | 01, 10         | 00, 11, 01, 10 | 00, 11 | 01, 10                | 00, 11, 01, 10 | 00, 11   |  |

| t     | 00, 11         | 10, 01, 11, 00 | 01, 10 | 10, 01                | 00, 11, 01, 10 | 11, 00   |  |

|       | T1*            | T1**           | T1***  | Type II               | Type IV        | Type III |  |

| t-1   | Type II        |                |        | Type I                |                |          |  |

|       | 01, 10         |                |        | 01, 10                |                |          |  |

| t     |                | 10, 01         |        | 00, 11                |                |          |  |

| t-1   | Type III       |                |        | Type I                |                |          |  |

|       | 00, 11         |                |        | 00, 11                |                |          |  |

| t     | 11, 00         |                |        | 01, 10                |                |          |  |

| t - 1 | Type IV        |                |        | Type I                |                |          |  |

|       | 00, 11, 01, 10 |                |        | 00, 11, 01, 10        |                |          |  |

| t     | 00, 11, 01, 10 |                |        | 10, 01, 11, 00        |                |          |  |

Defining

$$T_e = T_2 + T_1 - T_1^* (20)$$

we obtain the condition P''' < P as

$$T_e > \frac{(w-1)}{2}.$$

(21)

Similar to the analysis given for scheme II, we can approximate the condition P''' < P' as

$$T_2 + T_3 + T_4 + 2T_1^* < T_2 + T_3 + T_4 + 2T_1^{***}.$$

(22)

Using (9) and (20), we can rewrite (22) as

$$T_e > T_{\rm v}. \tag{23}$$

Also, we obtain the condition P''' < P'' as [see (13) and (19)]

$$T_2 + T_3 + T_4 + 2T_1^* < T_1 + 2T_4^{**}.$$

(24)

Now, define

$$T_r = T_3 + T_4 + T_1^*$$

and

$$T_e = T_2 + T_1 - T_1^*. (25)$$

Assuming the link width of w bits, the total transition between adjacent lines is w-1, and hence

$$T_e + T_r = w - 1.$$

(26)

Using (26), we can rewrite (24) as

$$2\left(T_2 - T_4^{**}\right) < 2T_e - w + 1. \tag{27}$$

The even inversion leads to power reduction when  $P^{'''} < P$ ,  $P^{'''} < P'$ , and  $P^{'''} < P''$ . Based on (21), (23), and (27), we obtain

$$T_e > \frac{(w-1)}{2}, \quad T_e > T_y, \quad 2(T_2 - T_4^{**}) < 2T_e - w + 1.$$

(28)

The full inversion leads to power reduction when P'' < P, P'' < P', and  $P'' < P^{'''}$ . Therefore, using (18) and (27), the full inversion condition is obtained as

$$2(T_2 - T_4^{**}) > 2T_y - w + 1, \quad (T_2 > T_4^{**})$$

$2(T_2 - T_4^{**}) > 2T_e - w + 1.$  (29)

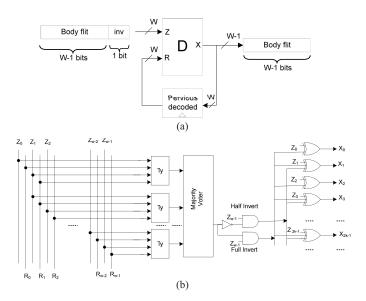

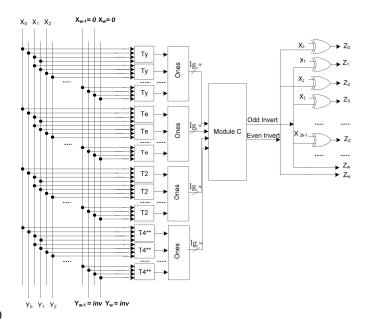

Fig. 4. Encoder architecture Scheme III.

Similarly, the condition for the odd inversion is obtained from P' < P, P' < P'', and  $P' < P^{'''}$ . Based on (16) and (23), the odd inversion condition is satisfied when

$$2(T_2 - T_4^{**}) < 2T_y - w + 1, \quad T_y > \frac{(w - 1)}{2}$$

$$T_e < T_y. \tag{30}$$

When none of (28), (29), or (30) is satisfied, no inversion will be performed.

2) Proposed Encoding Architecture: The operating principles of this encoder are similar to those of the encoders implementing Schemes I and II. The proposed encoding architecture, which is based on the even invert condition of (28), the full invert condition of (29), and the odd invert condition of (30), is shown in Fig. 4. The wth bit of the previously encoded body flit is indicated by inv which shows if it was even, odd, or full inverted (inv = 1) or left as it was (inv = 0). The first stage of the encoder determines the transition types while the second stage is formed by a set of 1s blocks which count the number of ones in their inputs. In the first stage, we have added the  $T_e$  blocks which determine if any of the transition types of  $T_2$ ,  $T_1^{**}$ , and  $T_1^{***}$  is detected for each pair bits of their inputs. For these transition types, the even invert action yields link power reduction. Again, we have four Ones blocks to determine the number of detected transitions for each  $T_y, T_e, T_2, T_4^{**}$ , blocks. The output of the Ones blocks are inputs for Module C. This module determines if odd, even, full, or no invert action corresponding to the outputs "10," "01," "11," or "00," respectively, should be performed. The outputs "01," "11," and "10" show that whether (28), (29), and (30), respectively, are satisfied. In this paper, Module C was designed based on the conditions given in (28), (29), and (30). Similar to the procedure used to design the decoder for scheme II, the decoder for scheme III may be designed.

Fig. 5. Percentage impact on silicon area and power dissipation of the network interface due to the data encoding/decoding logic.

#### V. RESULTS AND DISCUSSION

The proposed data encoding schemes have been assessed by means of a cycle-accurate NoC simulator based on Noxim [33]. The power estimation models of Noxim include NIs, routers, and links [25]. The link power dissipation was computed using (3) where the terms  $T_{0\rightarrow 1}$ ,  $T_1$ , and  $T_2$  were computed based on the information obtained from the cycleaccurate simulation. The following parameters were used in the simulations. The NoC was clocked at 700 MHz while the baseline NI with minimum buffering and supporting open core protocol 2 and advanced high-performance bus protocols [34] dissipated 5.3 mW. The average power dissipated by the wormhole-based router was 5.7 mW. Based on a 65-nm UMC technology, a total capacitance of 592 fF/mm was assumed for an inter-router wire. About 80% of this capacitance was due to the crosstalk. We assumed 2-mm 32-bit links and a packet size of 16 bytes (eight flits). Using the detailed simulations, when the flits traversed the NoC links, the corresponding selfand coupling switching activities were calculated and used along with the self- and coupling capacitance of 0.237 and 0.947 nf, respectively, to calculate the power ( $V_{\rm dd} = 0.9 \text{ V}$ and  $F_{ck} = 700 \text{ MHz}$ ).

## A. Overheads Due to the Encoder/Decoder Logic

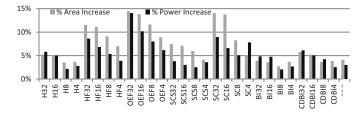

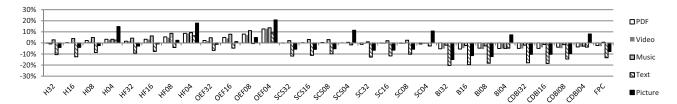

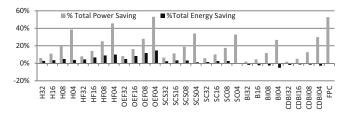

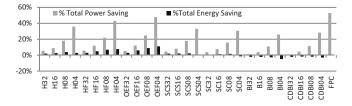

The encoder and the decoder were designed in Verilog HDL described at the RTL level, synthesized with synopsys design compiler and mapped onto an UMC 65-nm technology library. In our study, the area and power of the proposed encoding scheme I (H), scheme II (HF), and scheme III (OEF) are compared against SC and SCS [23], the BI coding [12], the coupling driven BI (CDBI) coding [26], and the forbidden pattern condition (FPC) codes [25]. The area and power overheads of the NI compared to the baseline NI are shown in Fig. 5. For each encoder type E, we consider four different implementations, denoted by  $E_4$ ,  $E_8$ ,  $E_{16}$ , and  $E_{32}$  where in  $E_n$ , the link is partitioned in 32/nn-bit sublinks. We apply the encoding scheme E in parallel to each sublink. In the case of FPC, 4-bit sublinks are used in this paper. The results of Fig. 5 reveal that the power overhead for all the encoding schemes is below 10%. Except for the cases of OEF 32 and OEF16, the area overhead is below 15%. As we will see later, in many cases, the link power saving achieved in the encoding is well above the overhead.

## B. Energy Analysis

To analyze the efficacy of the proposed data encoding schemes in reducing the energy consumption, we consider

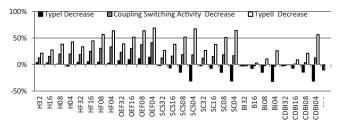

Fig. 6. Percentage of decrease Types I, II, and coupling switching activity obtained with different data encoding.

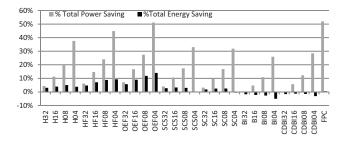

Fig. 7. Total power/energy saving using different data encoding schemes.

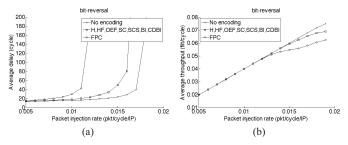

an 8 × 8 mesh-based NoC. We only report results for the bit-reversal traffic as for the other synthetic traffics we found similar trends. We assumed a minimum of two-flit and maximum eight-flit packets, deterministic XY routing, and input FIFO buffers of four flits. The simulations were run until 1 MB of traffic was drained by the network. The analysis has been performed using a different pir value for each data encoding scheme considered. Precisely, the pir value has been selected as the maximum pir sustainable by the particular data encoding scheme considered before entering to the saturation region (Figs. 11 and 12). That is, 0.016 when no data encoding is used, 0.010 for the FPC, and 0.013 for the remaining data encoding schemes. Random data patterns were considered.

Fig. 6 shows the decrease in the switching transitions of Types I, II, and coupling switching activity for different data encoding schemes compared to those of no data encoding. It shows that the proposed encoding schemes decreases both Types I and II. In the cases of previous encoding schemes (SCS, SC, BI, CDBI, and FPC) only Type II decreases while for some cases Type I even increases. In order to show the importance of Type I in decreasing the coupling transition activity, we compare the activities of OEF4 and SCS4. Both of them have the same effect on Type II while they have different effects on Type I. The difference leads to coupling transition activity reduction of 41% for OEF4 compared with 18% in the case of SCS4. Note that the coupling transition activity reduction is a weighted sum of the Types I and II transitions.

To obtain the results for total power and energy saving shown in Fig. 7, we have considered all the interconnect NoC components, including link, router, encoder, decoder, and NI. This part of NoC power/energy consumption constitutes an important fraction of the overall power/energy budget of the entire system [31]. The results indicate that for a given partitioning of the link (4, 8, 16, or 32 bits), except for BI32 and CDBI32, all of the schemes provide us with some power savings. Among them, OEF4 and FPC

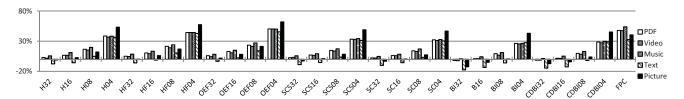

Fig. 8. Total power saving using different data encoding schemes for several data streams.

Fig. 9. Total energy saving using different data encoding schemes for several data streams.

show the highest power savings. This shows that our proposed schemes (along with the FPC technique) provide more power reductions when compared with other schemes. In the case of OEF4, we achieve the highest energy reduction of about 14%. All the proposed techniques provide some energy reductions. Among the schemes, BI and CDBI increase the total energy consumption. Interestingly, while the power reduction of FPC was impressive, its energy reduction is not noteworthy. This is due to the fact that this technique makes use of more than one control bit for coding. Since the bandwidth of the data transfer is fixed, having a higher number of control bits leads to a lower transfer rate of the actual data, increasing the number of flits, traffic, and the transfer time. Therefore, the total energy consumption increases for this scheme.

The power (energy) savings obtained when different data sets including PDF, video, music, text, and picture are used as the workloads are given in Fig. 8 (Fig. 9). As can be observed, when the partitioning is based on 4-bit width, all the three proposed schemes show energy savings for all the data streams considered in this paper. Also, in the case of OEF4, the saving is the largest among all the encoding schemes. For this encoding scheme, the maximum of energy and power more than 20% and 60%, respectively, was achieved for the picture workload.

Finally, it should be pointed out, in general, that the efficacy of any encoding schemes depends on workload data patterns which are transmitted via the bus. In the cases of the encoding techniques proposed in this paper, the switching activities of two consequent flits of the actual data affect the amount of savings. These activities may vary from one application to another. Higher (lower) activities provide more (fewer) opportunities for the power saving by the proposed encoding schemes. Specifically, if an application is dominated by integer computation, there could be cases that the MSB bits are not always toggled. This is due to the fact that the range of numbers may be limited, and hence, the sign bits may remain unchanged. Of course, this also depends on the representation of the signed numbers. For these applications, the proposed encoding schemes may provide lower power/energy savings. In these cases, one may apply the coding technique only to

Fig. 10. Increase of the completion time versus increase of power dissipation.

the bits with higher switching activities as has been performed for low-power memory addressing schemes (e.g., [22]).

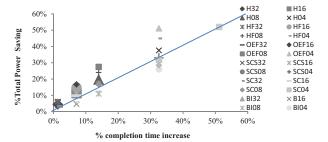

#### C. Power Versus Performance

The tradeoff between the reduction of the average power dissipation of the communication system with the completion time (i.e., the amount of the time needed to drain a given amount of traffic volume) is an important characteristic of the system. The percentage increase of completion time is defined as the percentage increase of the time needed to drain a given amount of traffic. In Fig. 10, this characteristic for each encoding scheme has been plotted. The average power dissipation improves almost for all encoding schemes that are considered in this paper. In this figure, the oblique line corresponds to equal percentages of power reduction and increased completion time. The points belonging to the lower (upper) region are characterized by a percentage of completion time increase which is greater (smaller) than the percentage of power dissipation reduction. From this graph, the OEF, HF, and H are the Pareto-optimal encoding schemes (i.e., are above the oblique line).

Let us now compare the average delay and the throughput of a baseline configuration (no data encoding) with a set of network configurations, where we use the proposed data encoding techniques. We assume 32-bit links and packets of four flits (flit size is 32 bits). The schemes H, HF, OEF, SC, SCS, and BI require one, two, four, and eight additional bits (inv bits) when the link is divided into one, two, four,

Fig. 11. (a) Average delay. (b) Throughput using different data coding.

Fig. 12. Total power/energy saving using different data encoding schemes.

and eight partitions, respectively. Thus, in the worst case (eight partitions), one additional flit is required to transfer the original four-flit payload. When the FPC is used, additional 11 bits are needed for each encoded flit. Thus, for a fourflit payload, we would have 44 additional bits, which require two additional flits. Fig. 11 shows the average delay and the throughput for different packet injection rates (pir) under the bit-reversal traffic scenario. Similar results are obtained with other traffic scenarios. Note that, in the case of the baseline implementation, the network saturation point occurs at a higher pir value as compared to the implementations which use data encoding. This is because, for a given pir, when a data encoding technique is used, other than the normal traffic injected into the network, there is also a traffic component related to the control information (in our case inv information) which increases the congestion level in the network. In the case of H, HF, OEF, SC, SCS, and the BI encoding techniques, the saturation point is only 10% lower than that of the baseline configuration. In terms of saturation point, the baseline implementation outperforms H, HF, OEF, SC, SCS, and BI implementations by 13%. For both the average delay and the throughput, the FPC method provides the worst results.

## D. Multimedia SoC Case Study

In this section, we analyze the efficacy of the proposed data encoding schemes on two complex heterogeneous systems. The first one, which is mapped to an 8 × 8 mesh, consisted of a triple video object plane decoder which has 38 cores (D 38 tvopd) [32] and multimedia and wireless communication which has 26 cores (D 26 media) [33]. We assumed a minimum of two-flit and maximum eight-flit packets, deterministic XY routing, and input FIFO buffers of four flits. The time distribution of the traffic followed Poisson's distribution while random data sets were used as workloads. The packet injection rates of the different communication flows have been determined using the bandwidth requirements reported in [32] and [33].

The results of power and energy saving when different data encoding schemes have been applied to this system are

Fig. 13. Total power/energy saving using different data encoding schemes.

presented in Fig. 12. For these results, we assumed that the packet size was eight flits. As can be observed from the results, the amount of power and energy reductions are similar to the results presented in Fig. 7 where we had assumed the bit-reversal traffic.

The second heterogeneous system consists of an MPEG-4 decoder, a picture-in-picture, a multiwindow display, a 263 encoder and mp3 decoder, and a 263 decoder and an mp3 decoder, which have a total of 58 cores [34]. The system is mapped to an  $8 \times 8$  mesh using the mapping technique described in [35]. We assumed the same parameters as those of the previous complex heterogeneous system. Also, the packet injection rates of the different communication flows were determined based on the bandwidth requirements reported in [34]. As the results presented in Fig. 13 show, all of the schemes provide some power savings. Among them, FPC and OEF4 show the highest power savings. For the total energy consumption result, the highest reduction of above 11% is achieved for OEF4. The amount of power and energy reductions for almost all the schemes are less than the corresponding results presented in Fig. 12. This is due to the fact that this system provides a shorter average hop count than the previous system. This lowers the effectiveness of the proposed data encoding techniques.

## VI. CONCLUSION

In this paper, we have presented a set of new data encoding schemes aimed at reducing the power dissipated by the links of an NoC. In fact, links are responsible for a significant fraction of the overall power dissipated by the communication system. In addition, their contribution is expected to increase in future technology nodes. As compared to the previous encoding schemes proposed in the literature, the rationale behind the proposed schemes is to minimize not only the switching activity, but also (and in particular) the coupling switching activity which is mainly responsible for link power dissipation in the deep submicronmeter technology regime. The proposed encoding schemes are agnostic with respect to the underlying NoC architecture in the sense that their application does not require any modification neither in the routers nor in the links. An extensive evaluation has been carried out to assess the impact of the encoder and decoder logic in the NI. The encoders implementing the proposed schemes have been assessed in terms of power dissipation and silicon area. The impacts on the performance, power, and energy metrics have been studied using a cycle- and bitaccurate NoC simulator under both synthetic and real traffic scenarios. Overall, the application of the proposed encoding

schemes allows savings up to 51% of power dissipation and 14% of energy consumption without any significant performance degradation and with less than 15% area overhead in the NI.

#### REFERENCES

- [1] International Technology Roadmap for Semiconductors. (2011) [Online]. Available: http://www.itrs.net

- [2] M. S. Rahaman and M. H. Chowdhury, "Crosstalk avoidance and errorcorrection coding for coupled RLC interconnects," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2009, pp. 141–144.

- [3] W. Wolf, A. A. Jerraya, and G. Martin, "Multiprocessor system-on-chip MPSoC technology," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 27, no. 10, pp. 1701–1713, Oct. 2008.

- [4] L. Benini and G. De Micheli, "Networks on chips: A new SoC paradigm," *Computer*, vol. 35, no. 1, pp. 70–78, Jan. 2002.

- [5] S. E. Lee and N. Bagherzadeh, "A variable frequency link for a power-aware network-on-chip (NoC)," *Integr. VLSI J.*, vol. 42, no. 4, pp. 479–485, Sep. 2009.

- [6] D. Yeh, L. S. Peh, S. Borkar, J. Darringer, A. Agarwal, and W. M. Hwu, "Thousand-core chips roundtable," *IEEE Design Test Comput.*, vol. 25, no. 3, pp. 272–278, May–Jun. 2008.

- [7] A. Vittal and M. Marek-Sadowska, "Crosstalk reduction for VLSI," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 16, no. 3, pp. 290–298, Mar. 1997.

- [8] M. Ghoneima, Y. I. Ismail, M. M. Khellah, J. W. Tschanz, and V. De, "Formal derivation of optimal active shielding for low-power on-chip buses," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 25, no. 5, pp. 821–836, May 2006.

- [9] L. Macchiarulo, E. Macii, and M. Poncino, "Wire placement for crosstalk energy minimization in address buses," in *Proc. Design Autom. Test Eur. Conf. Exhibit.*, Mar. 2002, pp. 158–162.

- [10] R. Ayoub and A. Orailoglu, "A unified transformational approach for reductions in fault vulnerability, power, and crosstalk noise and delay on processor buses," in *Proc. Design Autom. Conf. Asia South Pacific*, vol. 2. Jan. 2005, pp. 729–734.

- [11] K. Banerjee and A. Mehrotra, "A power-optimal repeater insertion methodology for global interconnects in nanometer designs," *IEEE Trans. Electron Devices*, vol. 49, no. 11, pp. 2001–2007, Nov. 2002.

- [12] M. R. Stan and W. P. Burleson, "Bus-invert coding for low-power I/O," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 3, no. 1, pp. 49–58, Mar. 1995.

- [13] S. Ramprasad, N. R. Shanbhag, and I. N. Hajj, "A coding framework for low-power address and data busses," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 7, no. 2, pp. 212–221, Jun. 1999.

- [14] C. L. Su, C. Y. Tsui, and A. M. Despain, "Saving power in the control path of embedded processors," *IEEE Design Test Comput.*, vol. 11, no. 4, pp. 24–31, Oct.–Dec. 1994.

- [15] L. Benini, G. De Micheli, E. Macii, D. Sciuto, and C. Silvano, "Asymptotic zero-transition activity encoding for address busses in low-power microprocessor-based systems," in *Proc. 7th Great Lakes Symp. VLSI*, Mar. 1997, pp. 77–82.

- [16] E. Musoll, T. Lang, and J. Cortadella, "Working-zone encoding for reducing the energy in microprocessor address buses," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 6, no. 4, pp. 568–572, Dec. 1998.

- [17] W. Fornaciari, M. Polentarutti, D. Sciuto, and C. Silvano, "Power optimization of system-level address buses based on software profiling," in *Proc. 8th Int. Workshop Hardw. Softw. Codesign*, May 2000, pp. 29–33.

- [18] L. Benini, G. De Micheli, E. Macii, M. Poncino, and S. Quer, "Power optimization of core-based systems by address bus encoding," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 6, no. 4, pp. 554–562, Dec. 1998.

- [19] L. Benini, A. Macii, M. Poncino, and R. Scarsi, "Architectures and synthesis algorithms for power-efficient bus interfaces," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 19, no. 9, pp. 969–980, Sep. 2000.

- [20] G. Ascia, V. Catania, M. Palesi, and A. Parlato, "Switching activity reduction in embedded systems: A genetic bus encoding approach," *IEE Proc. Comput. Digit. Tech.*, vol. 152, no. 6, pp. 756–764, Nov. 2005.

- [21] R. Siegmund, C. Kretzschmar, and D. Muller, "Adaptive Partial Businvert encoding for power efficient data transfer over wide system buses," in *Proc. 13th Symp. Integr. Circuits Syst. Design*, Sep. 2000, pp. 371–376.

- [22] S. Youngsoo, C. Soo-Ik, and C. Kiyoung, "Partial bus-invert coding for power optimization of application-specific systems," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 9, no. 2, pp. 377–383, Apr. 2001.

- [23] M. Palesi, G. Ascia, F. Fazzino, and V. Catania, "Data encoding schemes in networks on chip," *IEEE Trans. Comput.-Aided Design Integr. Circuits* Syst., vol. 30, no. 5, pp. 774–786, May 2011.

- [24] C. G. Lyuh and T. Kim, "Low-power bus encoding with crosstalk delay elimination," *IEE Proc. Comput. Digit. Tech.*, vol. 153, no. 2, pp. 93–100, Mar. 2006.

- [25] P. P. Pande, H. Zhu, A. Ganguly, and C. Grecu, "Energy reduction through crosstalk avoidance coding in NoC paradigm," in *Proc. 9th EUROMICRO Conf. Digit. Syst. Design Archit. Methods Tools*, Sep. 2006, pp. 689–695.

- [26] K. W. Ki, B. Kwang Hyun, N. Shanbhag, C. L. Liu, and K. M. Sung, "Coupling-driven signal encoding scheme for low-power interface design," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Design*, Nov. 2000, pp. 318–321.

- [27] L. Rung-Bin, "Inter-wire coupling reduction analysis of bus-invert coding," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 7, pp. 1911–1920, Aug. 2008.

- [28] Z. Khan, T. Arslan, and A. T. Erdogan, "Low power system on chip bus encoding scheme with crosstalk noise reduction capability," *IEE Proc. Comput. Digit. Tech.*, vol. 153, no. 2, pp. 101–108, Mar. 2006.

- [29] Z. Yan, J. Lach, K. Skadron, and M. R. Stan, "Odd/even bus invert with two-phase transfer for buses with coupling," in *Proc. Int. Symp. Low Power Electron. Design*, 2002, pp. 80–83.

- [30] C. P. Fan and C. H. Fang, "Efficient RC low-power bus encoding methods for crosstalk reduction," *Integr. VLSI J.*, vol. 44, no. 1, pp. 75–86, Jan. 2011.

- [31] S. R. Vangal, J. Howard, G. Ruhl, S. Dighe, H. Wilson, J. Tschanz, W. James, D. Finan, A. P. Singh, T. Jacob, S. Jain, V. Erraguntla, C. Roberts, Y. V. Hoskote, N. Y. Borkar, and S. Y. Borkar, "An 80-tile Sub-100-W TeraFLOPS processor in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 1, pp. 29–41, Jan. 2008.

- [32] S. Murali, C. Seiculescu, L. Benini, and G. De Micheli, "Synthesis of networks on chips for 3D systems on chips," in *Proc. Asia South Pacific Design Autom. Conf.*, Jan. 2009, pp. 242–247.

- [33] C. Seiculescu, S. Murali, L. Benini, and G. De Micheli, "SunFloor 3D: A tool for networks on chip topology synthesis for 3-D systems on chips," in *Proc. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 29, no. 12, pp. 1987–2000, Dec. 2010.

- [34] S. Murali and G. De Micheli, "Bandwidth-constrained mapping of cores onto NoC architectures," in *Proc. Design, Autom. Test Eur. Conf. Exhibit.*, vol. 2. Feb. 2004, pp. 896–901.

- [35] M. Palesi, R. Tornero, J. M. Orduñna, V. Catania, and D. Panno, "Designing robust routing algorithms and mapping cores in networks-onchip: A multi-objective evolutionary-based approach," *J. Univ. Comput.* Sci., vol. 18, no. 7, pp. 937–969, 2012.

Nima Jafarzadeh was born in Marand, Iran, in 1982. He received the Master of Computer Architecture degree from the Azad University Science and Research Branch, Tehran, Iran, 2009, where he is currently pursuing the Ph.D. degree from the Department of Computer Engineering.

His current research interests include network-onchips, low power interconnection, reliable interconnection, and analytical modeling.

**Maurizio Palesi** (M'06) received the M.S. and Ph.D. degrees in computer engineering from the Università di Catania, Catania, Italy, in 1999 and 2003, respectively.

He has been an Assistant Professor with Kore University, Enna, Italy, since 2010.

Dr. Palesi serves as the Technical Program Committee Member for the following IEEE/ACM International Conferences: RTAS, CODES+ISSS, DATE, NOCS, ESTIMedia, SOCC, VLSI, ISC, and SITIS. He was also the Co-organizer of International Work-

shops on Network-on-Chip Architectures in 2008, 2009, and 2010, respectively.

Ahmad Khademzadeh received the B.Sc. degree in applied physics from Ferdowsi University, Mashhad, Iran, in 1969, and the M.Sc. and Ph.D. degrees in digital communication and information theory and error control coding from the University of Kent, Kent, U.K.

He is currently the Head of Education and National Scientific and International Scientific Cooperation Department, Iran Telecom Research Center (ITRC), Tehran, Iran. He was the Head of Test Engineering Group and the Director of Computer and Commu-

nication Department, ITRC. He is also a Lecturer with Tehran Universities and is a Committee Member of the Iranian Electrical Engineering Conference Permanent Committee.

Dr. Khadem-Zadeh was selected as the National Outstanding Researcher of the Iran Ministry of Information and Communication Technology.

Ali Afzali-Kusha (SM'06) received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the Sharif University of Technology, Tehran, Iran, University of Pittsburgh, Pittsburgh, PA, USA, and the University of Michigan, Ann Arbor, MI, USA, in 1988, 1991, and 1994, respectively.

He was a Post-Doctoral Fellow with the University of Michigan, from 1994 to 1995. Since 1995, he has been with The University of Tehran, Tehran, where he is currently a Professor with the School of Electrical and Computer Engineering and the Director of

Low-Power High-Performance Nanosystems Laboratory. Also, on a research leave from the University of Tehran, Tehran, he has been a Research Fellow with the University of Toronto, Toronto, ON, Canada, and the University of Waterloo, Waterloo, ON, Canada, in 1998 and 1999, respectively. His current research interests include low-power high-performance design methodologies from the physical design level to the system level for nanoelectronics era.