# Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit

Partha Bhattacharyya, Senior Member, IEEE, Bijoy Kundu, Sovan Ghosh, Vinay Kumar, Member, IEEE, and Anup Dandapat, Member, IEEE

Abstract—In this paper, a hybrid 1-bit full adder design employing both complementary metal-oxide-semiconductor (CMOS) logic and transmission gate logic is reported. The design was first implemented for 1 bit and then extended for 32 bit also. The circuit was implemented using Cadence Virtuoso tools in 180and 90-nm technology. Performance parameters such as power, delay, and layout area were compared with the existing designs such as complementary pass-transistor logic, transmission gate adder, transmission function adder, hybrid pass-logic with static CMOS output drive full adder, and so on. For 1.8-V supply at 180-nm technology, the average power consumption (4.1563  $\mu$ W) was found to be extremely low with moderately low delay (224 ps) resulting from the deliberate incorporation of very weak CMOS inverters coupled with strong transmission gates. Corresponding values of the same were 1.17664  $\mu$ W and 91.3 ps at 90-nm technology operating at 1.2-V supply voltage. The design was further extended for implementing 32-bit full adder also, and was found to be working efficiently with only 5.578-ns (2.45-ns) delay and 112.79-µW (53.36-µW) power at 180-nm (90-nm) technology for 1.8-V (1.2-V) supply voltage. In comparison with the existing full adder designs, the present implementation was found to offer significant improvement in terms of power and speed.

Index Terms—Carry propagation adder, high speed, hybrid design, low power.

## I. INTRODUCTION

NCREASED usage of the battery-operated portable devices, cellular phones, personal digital assistants (PDAs), and notebooks demand VLSI, and ultra large-scale integration designs with an improved powerdelay characteristics. Full adders, being one of the most fundamental building block of all the aforementioned circuit applications, remain a key focus domain of the researchers over the years [1], [2]. Different logic styles, each having its own merits and bottlenecks, was investigated to implement 1-bit full adder cells [3]-[11]. The designs, reported so far, may be broadly classified into two categories: 1) static style and 2) dynamic style. Static full adders are generally more

Manuscript received August 5, 2013; revised June 27, 2014; accepted September 1, 2014.

P. Bhattacharyya, B. Kundu, and S. Ghosh are with the Department of Electronics and Telecommunication Engineering, Indian Institute of Engineering Science and Technology, Howrah 711103, India (e-mail: pb\_etc\_besu@yahoo.com; kundu.bijoy1989@gmail.com; sovanghosh10@gmail.com).

V. Kumar and A. Dandapat are with the Department of Electronics and Communication Engineering, National Institute of Technology Meghalaya, Shillong 793012, India (e-mail: vinaynits@gmail.com; anup.dandapat@gmail.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2014.2357057

reliable, simpler with less power requirement but the on chip area requirement is usually larger compared with its dynamic counterpart [3], [4].

Different logic styles tend to favor one performance aspect at the expense of others. Standard static complementary metal—oxide—semiconductor (CMOS) [3], dynamic CMOS logic [4], complementary pass-transistor logic (CPL) [5], [6], and transmission gate full adder (TGA) [7], [8] are the most important logic design styles in the conventional domain. The other adder designs use more than one logic style, known as hybrid-logic design style, for their implementation [9]. These designs exploit the features of different logic styles to improve the overall performance of the full adder.

The advantages of standard complementary (CMOS) style-based adders (with 28 transistors) are its robustness against voltage scaling and transistor sizing; while the disadvantages are high input capacitance and requirement of buffers [3]. Another complementary type smart design is the mirror adder [4] with almost same power consumption and transistor count (as that of [3]) but the maximum carry propagation path/delay inside the adder is relatively smaller than that of the standard CMOS full adder. On the other hand, CPL shows good voltage swing restoration employing 32 transistors [5], [6]. However, CPL is not an appropriate choice for low-power applications. Because of its high switching activity of intermediate nodes (increased switching power), high transistor count, static inverters, and overloading of its inputs are the bottleneck of this approach. The prime disadvantage of CPL, that is, the voltage degradation was successfully addressed in TGA, which uses only 20 transistors for full adder implementation [7], [8]. However, the other drawbacks of CPL like slow-speed and high-power consumption remain an area of concern for the researchers. Later, researchers focused on the hybrid logic approach which exploited the features of different logic styles in order to improve the overall performance. Vesterbacka [10] reported a 14-transistor full adder employing more than one logic style for their implementation. Similarly, the hybrid passlogic with static CMOS output drive full adder (HPSC) was proposed by Zhang et al. [11]. In such HPSC circuit, XOR, and XNOR functions were simultaneously generated by pass transistor logic module by using only six transistors, and employed in CMOS module to produce fullswing outputs of the full adder but at the cost of increased transistor count and decreased speed. Although the hybrid logic styles offers promising performance, most of these hybrid logic adders suffered from poor driving capability issue and

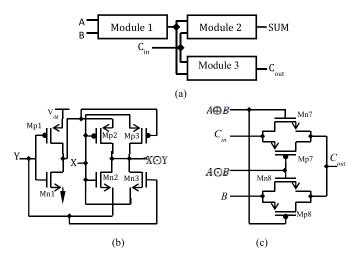

Fig. 1. (a) Schematic structure of proposed full adder. (b) XNOR module. (c) Carry generation module.

their performance degrades drastically in the cascaded mode of operation if the suitably designed buffers are not included. The main objective of this paper is to improve the different performance parameters like power, delay, and transistor count of the full adder compared with the already existing ones. The circuit was implemented using both 180- and 90-nm technology by using Cadence Virtuoso tools. The average power consumption (4.1563  $\mu$ W) of the proposed circuit was reduced dramatically by deliberate incorporation of very weak CMOS inverters coupled with strong transmission gates for 1.8 V supply when implemented at 180-nm technology. On the other hand, the layout area excluding buffer (102.94  $\mu$ m<sup>2</sup>) and the delay of the circuit (224 ps), in 180-nm technology, were comparable with the other hybridized implementations and better with respect to other full CMOS implementation, respectively. For 90-nm technology operated at 1.2-V power supply, the corresponding values are 1.17664  $\mu W$  (average power consumption), 91.3 ps (delay), and 25.84  $\mu$ m<sup>2</sup> (layout area excluding buffer). The design was verified and proved to be also promising for 32-bit carry propagation adder.

#### II. DESIGN APPROACH OF THE PROPOSED FULL ADDER

The proposed full adder circuit is represented by three blocks as shown in Fig. 1(a). Module 1 and module 2 are the XNOR modules that generate the sum signal (SUM) and module 3 generates the output carry signal ( $C_{\rm out}$ ). Each module is designed individually such that the entire adder circuit is optimized in terms of power, delay, and area. These modules are discussed below in detail.

# A. Modified XNOR Module

In the proposed full adder circuit, XNOR module is responsible for most of the power consumption of the entire adder circuit. Therefore, this module is designed to minimize the power to the best possible extend with avoiding the voltage degradation possibility. Fig. 1(b) shows the modified XNOR circuit where the power consumption is reduced significantly by deliberate use of weak inverter (channel width of transistors being small) formed by transistors Mp1

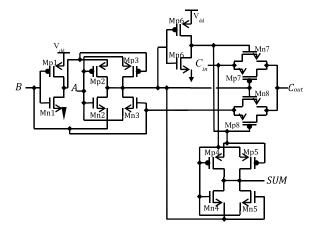

Fig. 2. Detail circuit diagram of proposed full adder.

and Mn1 [Fig. 1(b)]. Full swing of the levels of output signals is guaranteed by level restoring transistors Mp3 and Mn3 [Fig. 1(b)]. Various XOR/XNOR topologies have already been reported in [7] and [12]–[14]. The XOR/XNOR reported in [12]–[14] uses four transistors but at the cost of low logic swing. To the contrary, the XOR/XNOR reported in [7] uses six transistors to get better logic swing compared with that of 4 T XOR/XNOR [12]–[14]. In this paper also, the XNOR module employed 6 T, but having different transistor arrangement than that of 6 T XOR/XNOR [7]. The modified XNOR presented in this paper offers low-power and high-speed (with acceptable logic swing) compared with 6 T XOR/XNOR [7].

#### B. Carry Generation Module

In the proposed circuit, the output carry signal is implemented by the transistors Mp7, Mp8, Mn7, and Mn8 as shown in Fig. 1(c). The input carry signal ( $C_{in}$ ) propagates only through a single transmission gate (Mn7 and Mp7), reducing the overall carry propagation path significantly. The deliberate use of strong transmission gates (channel width of transistors Mn7, Mp7, Mn8, and Mp8 is made large) guaranteed further reduction in propagation delay of the carry signal.

# III. OPERATION OF THE PROPOSED FULL ADDER WITH SIMULATION TEST BENCH SETUP

Fig. 2 shows the detail diagram of the proposed full adder. The sum output of the full adder is implemented by XNOR modules. The inverter comprised of transistors Mp1 and Mn1 generate B', which is effectively used to design the controlled inverter using the transistor pair Mp2 and Mn2. Output of this controlled inverter is basically the XNOR of A and B. But it has some voltage degradation problem, which has been removed using two pass transistors Mp3 and Mn3. pMOS transistors (Mp4, Mp5, and Mp6) and nMOS transistors (Mn4, Mn5, and Mn6) realize the second stage XNOR module to implement the complete SUM function. Analyzing the truth table of a full adder, the condition for  $C_{\rm out}$  generation has been deducted as follows:

If,

$$A = B$$

, then  $C_{\text{out}} = B$ ; else,  $C_{\text{out}} = C_{\text{in}}$ .

Fig. 3. Simulation test bench setup.

The parity between inputs A and B is checked by  $A \odot B$  function. If they are same, then  $C_{\text{out}}$  is same as B, which is implemented using the transmission gate realized by transistors Mp8 and Mn8. Otherwise, the input carry signal  $(C_{\text{in}})$  is reflected as  $C_{\text{out}}$  which is implemented by another transmission gate consisting of transistors Mp7 and Mn7.

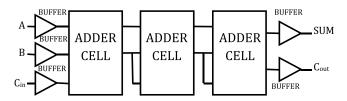

It is likely that a single bit adder cell designed for optimum performance may not perform well under deployment to realtime conditions. This is because when connected in cascaded form, the driver adder cells may not provide proper input signal level to the driven cells. The cumulative degradation in signal level may lead to faulty output and the circuit may malfunction under low supply voltages. To analyze the success of the proposed full adder during its actual use in VLSI applications, a practical simulation environment is setup as shown in Fig. 3. To provide a realistic environment, buffers are added at the input and the output of the test bench [18], [25]. The inputs to the adder cell, are fed through the buffers to incorporate the effect of input capacitance and the outputs are also loaded with buffers to ensure proper loading condition. The proposed full adder is simulated using several test bench setups. These test benches are having the common prototype of three buffers at the input and two buffers at the output (Fig. 3). They only differed in the number of stages of adder cells used in between the input and output of the simulation setup. The number of stages varied starting from two and increased gradually. It was observed that the carry propagation delay from the input to the output started rising significantly in the order of two after the third stage (explained in detail in Section IV-B). Therefore, the three-stage simulation test bench is selected for simulation purpose. Further, the behavior of performance parameters (power and delay) could be measured from the second adder cell by using this test bench. This offered the tested adder cell to have the output and input capacitances of adjacent adder cells as its input and output capacitance; allowing a real time simulation environment for cascaded approach. Numerous random signal patterns were applied at the inputs and the worst case simulation results of the second full adder cell was accounted for analysis and comparison. The performance analysis of the proposed full adder was performed with variation in supply voltage both for 180- and 90-nm technology.

# IV. PERFORMANCE ANALYSIS OF THE PROPOSED FULL ADDER

The simulation of the proposed full was carried out using both 90- and 180-nm technology and compared with the other potential adder designs reported in [1]–[11] and [15]–[24] with special emphasis on the hybrid design approach [1], [2], [19].

$\label{eq:table_interpolation} TABLE\ I$  Transistor Sizes of Proposed Full Adder

| Transistor<br>Name | 180nm technology |            | 90nm technology |            |

|--------------------|------------------|------------|-----------------|------------|

|                    | Width (W)        | Length (L) | Width (W)       | Length (L) |

|                    | (nm)             | (nm)       | (nm)            | (nm)       |

| Mn1, Mn6           | 400              | 180        | 120             | 90         |

| Mp1, Mp6           | 800              | 180        | 240             | 90         |

| Mn2, Mn3           | 400              | 180        | 120             | 90         |

| Mp2, Mp3           | 800              | 180        | 360             | 90         |

| Mn4, Mn5           | 400              | 180        | 120             | 90         |

| Mp4, Mp5           | 400              | 180        | 120             | 90         |

| Mn7, Mn8           | 400              | 180        | 360             | 90         |

| Mp7, Mp8           | 400              | 180        | 600             | 90         |

TABLE II  $\label{table simulation} Simulation Results for Full Adders in 180 \ nm$   $Technology \ With 1.8 \ V \ Supply$

| Design            | Average<br>Power<br>(µw) | Delay<br>(ps) | PDP<br>(fJ) | Transistor<br>Count | Reference |

|-------------------|--------------------------|---------------|-------------|---------------------|-----------|

| C-CMOS            | 6.2199                   | 292.1         | 1.816832    | 28                  | [4,18]    |

| Mirror            | 6.0797                   | 281.61        | 1.712104    | 28                  | [18]      |

| CPL               | 7.71985                  | 183.97        | 1.42022     | 32                  | [5, 6]    |

| TFA               | 8.2491                   | 287.1         | 2.368316    | 16                  | [21]      |

| TGA               | 8.4719                   | 293.9         | 2.8989      | 20                  | [7, 8]    |

| 14 T              | 12.7217                  | 381.7         | 4.85587     | 14                  | [10]      |

| 10 T              | 14.3449                  | 132.59<br>5   | 1.902062    | 10                  | [24]      |

| HPSC              | 6.3798                   | 273.7         | 1.74615     | 22                  | [11]      |

| Majority<br>Based | 6.3227                   | 185.4         | 1.17222     |                     | [23]      |

| 24T               | 15.91                    | 314.2         | 4.998       | 24                  | [1]       |

| FA_Hybrid         | 5.978                    | 252.3         | 1.508       | 24                  | [2]       |

| FA_DPL            | 19.56                    | 226.6         | 4.432       | 22                  | [19]      |

| FA_SR-<br>CPL     | 20.78                    | 220.65        | 4.585       | 20                  | [19]      |

| Proposed          | 4.1563                   | 224           | 0.931       | 16                  | [Present] |

With an aim to optimize both power and delay of the circuit, the power-delay product (PDP), that is, the energy consumption has been minimized in the proposed case. It was observed that in the present design, the power consumption could be minimized by mainly sizing the transistors in inverter circuits; while the carry propagation delay could be improved by mainly sizing the transistors of the transmission gates present between the paths from  $C_{\rm in}$  to  $C_{\rm out}$ . The transistor sizes of the proposed full adder circuit are given in Table I for both the technologies (90 and 180 nm). Power consumption, propagation delay, and PDP of the proposed full adder along with that of existing full adders (from literature) are given in Tables II and III for 180-nm and 90-nm technology, respectively.

For comparison in a common environment, the proposed full adder as well as the other reported ones, as cited in Tables I–III, were simulated using the common test bench. The simulation was performed for varying supply voltage ranging from 0.8 to 2.5 V (0.6–1.5 V) in 180-nm (90-nm) technology. The performance result of 10 T [24] full adder is unavailable in Table III, because it is nonoperable with

TABLE III

SIMULATION RESULTS FOR FULL ADDERS IN 90 nm

TECHNOLOGY WITH 1.2 V SUPPLY

| Designs           | Average<br>Power(µW) | Delay<br>(ns) | PDP(fJ)  | Transistor<br>Count | Reference |

|-------------------|----------------------|---------------|----------|---------------------|-----------|

| C-CMOS            | 1.5799               | 0.1269        | 0.200489 | 28                  | [4,18]    |

| Mirror            | 1.5701               | 0.1226        | 0.19249  | 28                  | [18]      |

| CPL               | 1.7598               | 0.0791        | 0.1392   | 32                  | [5,6]     |

| TFA               | 1.7363               | 0.3198        | 0.55526  | 16                  | [21]      |

| TGA               | 1.7619               | 0.2317        | 0.40823  | 20                  | [7,8]     |

| 14T               | 3.3297               | 0.3389        | 1.12843  | 14                  | [10]      |

| 10T               |                      |               |          | 10                  | [24]      |

| HPSC              | 1.56                 | 0.2207        | 0.34429  | 22                  | [11]      |

| Majority<br>Based | 1.5751               | 0.0939        | 0.1479   |                     | [23]      |

| 24T               | 7.707                | 0.1406        | 1.0836   | 24                  | [1]       |

| FA_Hybrid         | 6.21                 | 0.143         | 0.888    | 24                  | [2]       |

| FA_DPL            | 7.34                 | 0.254         | 1.864    | 22                  | [19]      |

| FA_SR-<br>CPL     | 7.4                  | 0.167         | 1.235    | 20                  | [19]      |

| Proposed          | 1.17664              | 0.0913        | 0.107427 | 16                  | [Present] |

1.2 V at 90-nm technology [24]. The majority-based adder, reported by Navi *et al.* [23], included capacitors in their design, hence avoided to maintain the uniformity of the comparison.

The proposed hybrid full adder has also been compared with other hybrid full adders reported in [1], [2], and [19]. The circuit of the hybrid full adder reported in [1], [2], and [19] were resimulated in cadence virtuoso tools in 180- and 90-nm technology, so this paper can be authentically compared. The proposed hybrid adder requires only 16 transistors whereas the other hybrid adders [1], [2], [19] require more than 20 transistors. The average power consumed by the proposed full adder is significantly lower than that of other hybrid full adders. The use of less number of transistors in this paper also improved the speed. Because of reduction in average power consumption and propagation delay, the PDP of the proposed hybrid full adder is significantly improved in comparison with the earlier hybrid adders. The detailed comparison of the proposed full adder with other hybrid full adders [1], [2], [19] in 180- and 90-nm technology is represented in Tables II and III, respectively.

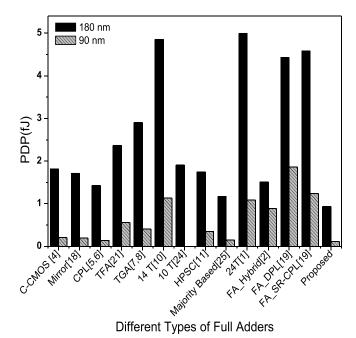

The performance of the proposed full adder in terms of power consumption and propagation delay with variation in supplied voltage was carried out (not shown here) and the corresponding comparison of the PDP (with the other existing designs) is shown in Fig. 4. The optimization of power consumption and propagation delay of the proposed full adder is explained in detail with necessary mathematical calculations in Sections IV-A and IV-B.

# A. Calculation of Power Consumption

Power consumption of the hybrid full adder can be broadly classified into two categories: 1) static power and 2) dynamic and short-circuit power [15]–[17].

Fig. 4. Comparison of PDP of various full adder designs.

Static power, originated from biasing and leakage currents, in most of the CMOS-based implementations is fairly low when compared with its dynamic counterpart [3]. In this paper, with an aim to minimize the static power further, the weak inverters having large channel width of 800/240 nm (in 180/90-nm technology) for Mp1 and Mp6, respectively, and 400/120 nm (180/90-nm technology) for Mn1 and Mn6, respectively (Fig. 2), was incorporated deliberately. The overall static power in 180-nm technology was found to be 2.139 nW for 1.8-V supply which is very low when compared with the overall dynamic power (4.1563  $\mu$ W). To the contrary, the static power in 90-nm technology at 1.2-V supply was found to be 0.936 nW which is also lower than the corresponding dynamic power (1.17664  $\mu$ W) but the ratio (of static power:dynamic power) increased. This increase in static power is possibly due to the increase in the subthreshold conduction current and gate leakage [3].

The dominant component of the power consumption, the dynamic power, arises because of charging and discharging of the load capacitances. The load capacitance,  $C_{\text{load}}$ , can be expressed as a combination of a fixed capacitance,  $C_{\text{fix}}$ , and a variable capacitance,  $C_{\text{var}}$ , as follows:

$$C_{\text{load}} = C_{\text{fix}} + C_{\text{var}}.$$

(1)

In this expression,  $C_{\rm fix}$  is the technology-dependent (principally originated from diffusion capacitance) and interconnect dependent capacitances. The interconnect dependent capacitance is minimized by efficient layout design in this case. On the other hand,  $C_{\rm var}$  is composed of the input capacitances of subsequent stages and a part of the diffusion capacitance at the gate output and can therefore be taken care of by proper sizing of the transistors.

For every low-to-high logic transition in an adder,  $C_{\rm load}$  incurs a voltage change  $\Delta V$ , drawing energy ( $C_{\rm load}*\Delta V*V_{\rm DD}$ ) from the supply voltage  $V_{\rm DD}$ . For each node j belongs

to N, these transitions occur at a fraction  $\alpha_j$  of the clock frequency  $f_c$ . So the total dynamic switching power can be calculated by summing over all N nodes in the circuit

Power =

$$V_{\text{DD}} * f_c * \sum_{j=1}^{N} \alpha_j * C_{\text{load}j} * \Delta V_j$$

. (2)

It is clear from (2) that the transistor size could be an effective parameter for reducing dynamic power consumption. Also, the inverters have to be weak and the transmission gates have to be strong. Initially, the transistor sizes were chosen on the theoretical background of the design. Subsequently, they were varied (through simulations) in the vicinity of the previously set values to obtain the best performance in terms of power and delay. The optimized transistor sizes of the proposed full adder are already summarized in Table I.

It was observed that the static power of the developed circuit varied from 56.38 to 392.4 pW for variation in supply voltage from 0.8 to 2.5 V in 180-nm technology. In contrast, the dynamic power varied from 114.08 nW to 6.125  $\mu$ W for the same voltage variation. Considering the similar kind of implementation using 90-nm technology with a voltage range of 0.6–1.5 V, the dynamic power consumption was found to be reduced dramatically while the static power consumption increased in comparison with the 180-nm case [Fig. 4(b)]. It is worth mentioning here that at 180-nm technology, the threshold voltage is 0.7-0.8 V and the MOSFET break down takes place after 2.5 V. So voltage was varied from 0.8 to 2.5 V in 180-nm node. On the other hand, at 90-nm technology, the threshold voltage is 0.6 V and the MOSFET break down occurs at 1.5 V. So, the voltage was varied from 0.6 to 1.5 V in the 90-nm case.

# B. Calculation of Propagation Delay

Because adder is the fundamental computational unit in most of the systems, its delay predominantly governs the overall speed performance of the entire system. Also, the speed of response of an adder is mainly dependent on the propagation delay of the carry signal which is usually minimized by reducing path length of the carry signal. In the present design, the carry signal is generated by controlled transmission of the input carry signal and either of the input signals A or B (when A = B). As the carry signal propagates only through the single transmission gate, the carry propagation path is minimized leading to a substantial reduction in propagation delay. The delay incurred in the propagation is further reduced by efficient transistor sizing and deliberate incorporation of strong transmission gates.

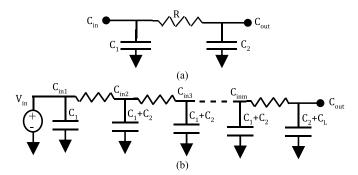

However, during cascaded operation of the proposed full adder, operating in the carry propagation mode, the speed performance of the adder deteriorates with increase in the number of adder stages. Similar observations were also reported in case of other transmission gate-based approaches. The transmission gate between signals  $C_{\rm in}$  and  $C_{\rm out}$  as shown in Fig. 2 will be in the ON state, and can be represented by R-C equivalent circuit as shown in Fig. 5(a), consisting of a linear resistance, R and parasitic capacitances at the input and output node,  $C_1$  and  $C_2$ , respectively [20].

Fig. 5. (a) Equivalent circuit of the transmission gate responsible for carry generation. (b) Equivalent circuit of *m* stage-cascaded proposed full adder.

Hence, such cascaded full adders (proposed design) operating in carry propagation mode (carry propagation adder) loaded with capacitance  $C_L$  can be represented by its equivalent R-C circuit as shown in Fig. 5(b).

Assuming the voltage source,  $V_{\rm in}$ , to be a step waveform (for simplicity), the delay  $\tau_{\rm pd}(m)$  of the cascaded proposed full adders, can be evaluated by simplifying it into a first-order circuit having a time constant,  $\tau$ , and applying the Elmore delay approximation [3] as follows:

$$\tau_{\rm pd}(m) = 0.69 \left[ R(C_1 + C_2) \frac{m(m+1)}{2} + mR(C_L - C_1) \right].$$

(3)

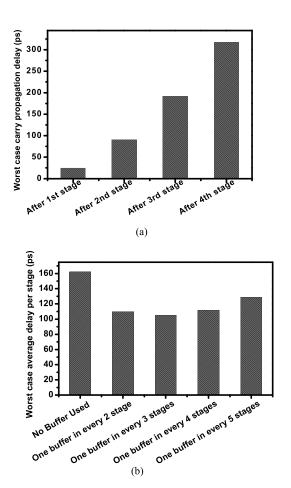

It is seen from (3) that the propagation delay of the proposed adder increases rapidly with the increase in the length of the adder chain (increases as the square of m). The simulation results incorporating the gradual increase in the number of stages of full adders also validated this second order rise in delay with increase in the number of stages [Fig. 6(a)]. The simulation results [given in Fig. 6(a)] were measured for no load capacitance (180-nm technology) and the worst case carry propagation delay is represented here. Incorporation of the load capacitance increased the delay but the nature of the graph remained the same. To minimize the overall delay, the buffers were included at appropriate stages of full adder chain. For efficient incorporation of buffers at appropriate stages, analytical evaluation was performed by extracting capacitance and resistance values from the postlayout simulation results.

Considering (3) and intermediate buffer delay, the total carry propagation delay for m stages after the incorporation of intermediate buffers can be represented as

$$\tau_{\rm pd}(m)_{\rm total} = \tau_{\rm pd}(m) + \tau_{\rm pdbuf}

= 0.69 \Big[ R(C_1 + C_2) \frac{m(m+1)}{2} + mR(C_{\rm inbuf} - C_1) \Big]

+ \tau_{\rm pdbuf}.$$

(4)

The load capacitance,  $C_L$ , of the adder chain is given in (3) is equal to the input capacitance,  $C_{\rm inbuf}$ , of the intermediate buffer and have been replaced to derive (4). The delay of the buffers,  $t_{\rm pdbuf}$ , is independent of the number of stages, m, and its value is obtained by intermediate delay calculation which is found to be 326.26 ps.

For the proposed full adder, the  $C_{\rm in}$  to  $C_{\rm out}$  path ON resistances and parasitic capacitances values extracted

Fig. 6. (a) Total carry propagation delay for different stages (without load capacitance). (b) Variation of average delay with introduction of buffers at different stages.

from postlayout simulation are as follows:

$$R_1 = 4.2365 \text{ k}\Omega$$

,  $C_1 = 13.792 \text{ fF}$  and  $C_2 = 6.689 \text{ fF}$ .

To find the optimized number of stages, the average delay per stage  $(\tau_{pd}(m)_{total})/m$ , value was minimized.

Differentiating this average delay value with respect to m, the expression for the minimum value of m is obtained as follows:

$$m = \sqrt{\frac{2 * \tau_{\text{pdbuf}}}{0.069 * R * (C_1 + C_2)}}.$$

(5)

The minimum value of m is evaluated from (5) which turns out to be 3.26 ( $\sim$ 3). The appropriate number of stages, m, for achieving the minimum carry propagation delay is further authenticated by the practical simulation results as shown in Fig. 6(b). From Fig. 6(b) and the mathematical result obtained from (5), it can be envisaged that the most optimized performance, when speed is of prime concern, is achieved using one buffer after every three stages.

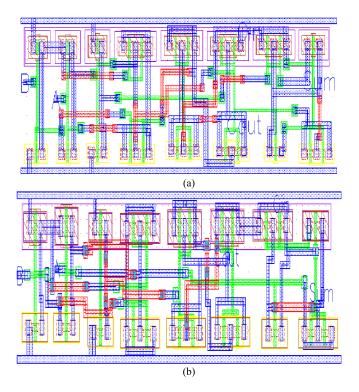

# C. Calculation of Area of 1-bit Adder

Fig. 7(a) and (b) shows the layout of the proposed full adder (excluding buffers) in 180- and 90-nm technology, respectively. The area in 180-nm technology is 102.94  $\mu$ m<sup>2</sup> and the

Fig. 7. (a) Layout of the 1-bit full adder in 180-nm technology. (b) Layout of the 1-bit full adder in 90-nm technology.

same was found to be 25.84  $\mu$ m<sup>2</sup> in 90-nm technology. The number of transistors for the proposed hybrid full adder including buffer is 36. Hence, the area of the layout of the proposed adder including buffer in 180-nm technology is 218.02  $\mu$ m<sup>2</sup> and the same in 90-nm technology is 49.36  $\mu$ m<sup>2</sup>. With an aim to enhance the performance of the proposed full adder in terms of power consumption and delay, the design required strong transmission gates and weak inverters. Therefore, the channel width of transistors Mp7, Mp8, Mn7, and Mn8 (involved in transmission gates) and transistors Mp1, Mp6, Mn1, and Mp6 (involved in inverters) (Fig. 2) were made relatively larger and smaller, respectively. The layout area (excluding buffer) in the present design is higher (6.55%) than that of TFA which is also comprised 16 transistors [21]. When compared with the best design in terms of area (10 T) [24], the proposed design of the adder (excluding buffer) consumed 44.5% more area. But, the main concern of the proposed adder design was minimization of PDP, which proved to be significantly improved ( $\sim$ 51%) with respect to 10 T design [24].

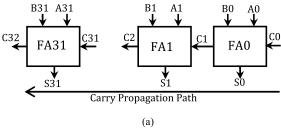

### V. Performance of 32-bit Full Adder

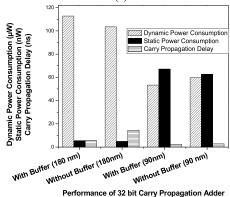

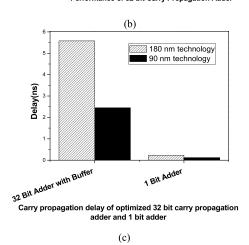

A 32-bit carry propagation adder [Fig. 8(a)] is implemented as an extension of the proposed 1-bit full adder. It is a noncarry look-ahead adder structure where the carry propagation takes place all the way to the last adder block. The performance evaluation of this 32-bit adder was also carried out in 180-and 90-nm technology with and without using intermediate buffers at appropriate stages. The incorporation of appropriate adder stages was done from the concluding result drawn from (5). Both power consumption and carry propagation

Fig. 8. (a) 32-bit full adder using 1-bit full adder. (b) Performance (power and delay) of 32-bit carry propagation adder with and without buffer with supply voltage of 1.8 V/1.2 V for 180 nm/90 nm. (c) Behavior of carry propagation delay when extended from proposed 1-bit full adder to 32-bit carry propagation adder.

delay was improved after using buffer; however, the delay improvement was more significant. The performance of this 32-bit full adder at 100 MHz and supply voltage of 1.8 V (180-nm technology) and 1.2 V (90-nm technology) is shown in Fig. 8(b). The difference in static and dynamic power consumption is large in 180-nm technology. But, this difference was somewhat reduced in 90-nm technology because of increase in the subthreshold conduction current and gate leakage [3]. Fig. 8(c) shows the behavior of the carry propagation delay when extended from 1 to 32 bits. It is observed that the carry propagation delay increased almost linearly with respect to the proposed 1-bit full adder.

### VI. CONCLUSION

In this paper, a low-power hybrid 1-bit full adder has been proposed the design has been extended for 32-bit case also. The simulation was carried out using standard Cadence Virtuoso tools with 180/90-nm technology and compared with other standard design approaches like CMOS, CPL, TFA, TGA, and other hybrid designs. The simulation results established that the proposed adder offered improved PDP compared with the earlier reports. The efficient coupling of strong transmission gates driven by weak CMOS inverters lead to fast switching speeds (224 ps at 1.8-V supply), for a layout area of 102.94  $\mu$ m<sup>2</sup> (in 180-nm technology) excluding buffer. The proposed full adder offered 20.56% improvement with respect to the best reported design [23] in terms of PDP (180-nm technology at 1.8 V). Corresponding PDP improvement was 27.36% when the same design was implemented in 90-nm technology at 1.2-V power supply. The proposed full adder was further used to implement a 32-bit carry propagation adder having buffers at appropriate adder stages (after three stages).

#### ACKNOWLEDGMENT

The authors would like to thank the School of VLSI Technology, Indian Institute of Engineering Science and Technology, Howrah, India, for providing the simulation facility.

#### REFERENCES

- [1] C.-K. Tung, Y.-C. Hung, S.-H. Shieh, and G.-S. Huang, "A low-power high-speed hybrid CMOS full adder for embedded system," in *Proc. IEEE Conf. Design Diagnostics Electron. Circuits Syst.*, vol. 13. Apr. 2007, pp. 1–4.

- [2] S. Goel, A. Kumar, and M. A. Bayoumi, "Design of robust, energy-efficient full adders for deep-submicrometer design using hybrid-CMOS logic style," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 14, no. 12, pp. 1309–1321, Dec. 2006.

- [3] N. H. E. Weste, D. Harris, and A. Banerjee, CMOS VLSI Design: A Circuits and Systems Perspective, 3rd ed. Delhi, India: Pearson Education, 2006.

- [4] J. M. Rabaey, A. Chandrakasan, and B. Nikolic, *Digital Integrated Circuits: A Design Perspective*, 2nd ed. Delhi, India: Pearson Education, 2003.

- [5] D. Radhakrishnan, "Low-voltage low-power CMOS full adder," IEE Proc.-Circuits Devices Syst., vol. 148, no. 1, pp. 19–24, Feb. 2001.

- [6] R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 1079–1090, Jul. 1997.

- [7] C. H. Chang, J. M. Gu, and M. Zhang, "A review of 0.18-μm full adder performances for tree structured arithmetic circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 13, no. 6, pp. 686–695, Jun. 2005.

- [8] A. M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 10, no. 1, pp. 20–29, Feb. 2002.

- [9] M. L. Aranda, R. Báez, and O. G. Diaz, "Hybrid adders for high-speed arithmetic circuits: A comparison," in *Proc. 7th IEEE Int. Conf. Elect. Eng. Comput. Sci. Autom. Control (CCE)*, Tuxtla Gutierrez, NM, USA, Sep. 2010, pp. 546–549.

- [10] M. Vesterbacka, "A 14-transistor CMOS full adder with full voltageswing nodes," in *Proc. IEEE Workshop Signal Process. Syst. (SiPS)*, Taipei, Taiwan, Oct. 1999, pp. 713–722.

- [11] M. Zhang, J. Gu, and C.-H. Chang, "A novel hybrid pass logic with static CMOS output drive full-adder cell," in *Proc. Int. Symp. Circuits Syst.*, May 2003, pp. 317–320.

- [12] S. Wairya, G. Singh, R. K. Nagaria, and S. Tiwari, "Design analysis of XOR (4T) based low voltage CMOS full adder circuit," in *Proc. IEEE Nirma Univ. Int. Conf. Eng. (NUICONE)*, Dec. 2011, pp. 1–7.

- [13] S. Goel, M. Elgamel, and M. A. Bayoumi, "Novel design methodology for high-performance XOR-XNOR circuit design," in *Proc. 16th Symp. Integr. Circuits Syst. Design (SBCCI)*, Sep. 2003, pp. 71–76.

- [14] J.-M. Wang, S.-C. Fang, and W.-S. Feng, "New efficient designs for XOR and XNOR functions on the transistor level," *IEEE J. Solid-State Circuits*, vol. 29, no. 7, pp. 780–786, Jul. 1994.

- [15] P. Prashanth and P. Swamy, "Architecture of adders based on speed, area and power dissipation," in *Proc. World Congr. Inf. Commun. Technol. (WICT)*, Dec. 2011, pp. 240–244.

- [16] M. J. Zavarei, M. R. Baghbanmanesh, E. Kargaran, H. Nabovati, and A. Golmakani, "Design of new full adder cell using hybrid-CMOS logic style," in *Proc. 18th IEEE Int. Conf. Electron., Circuits Syst. (ICECS)*, Dec. 2011, pp. 451–454.

- [17] I. Hassoune, D. Flandre, I. O'Connor, and J. Legat, "ULPFA: A new efficient design of a power-aware full adder," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 8, pp. 2066–2074, Aug. 2010.

- [18] K. Navi, M. Maeen, V. Foroutan, S. Timarchi, and O. Kavehei, "A novel low-power full-adder cell for low voltage," *VLSI J. Integr.*, vol. 42, no. 4, pp. 457–467, Sep. 2009.

- [19] M. Aguirre-Hernandez and M. Linares-Aranda, "CMOS full-adders for energy-efficient arithmetic applications," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 19, no. 4, pp. 718–721, Apr. 2011.

- [20] J. L. Wyatt, Jr., "Signal propagation delay in RC models for interconnect," in *Circuit Analysis, Simulation and Design, Part II, VLSI Circuit Analysis and Simulation*, vol. 3, A. Ruehli, Ed. Amsterdam, The Netherlands: North Holland, 1987, ch. 11.

- [21] M. Alioto, G. Di Cataldo, and G. Palumbo, "Mixed full adder topologies for high-performance low-power arithmetic circuits," *Microelectron. J.*, vol. 38, no. 1, pp. 130–139, Jan. 2007.

- [22] X. Wu and F. Prosser, "Design of ternary CMOS circuits based on transmission function theory," *Int. J. Electron.*, vol. 65, no. 5, pp. 891–905, 1988.

- [23] K. Navi, M. H. Moaiyeri, R. F. Mirzaee, O. Hashemipour, and B. M. Nezhad, "Two new low-power full adders based on majority-not gates," *Microelectron. J.*, vol. 40, no. 1, pp. 126–130, Jan. 2009.

- [24] H. T. Bui, Y. Wang, and Y. Jiang, "Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 49, no. 1, pp. 25–30, Jan. 2002.

- [25] K. Navi et al., "A novel low-power full-adder cell with new technique in designing logical gates based on static CMOS inverter," *Microelectron*. J., vol. 40, no. 10, pp. 1441–1448, Oct. 2009.

Partha Bhattacharyya (M'10–SM'14) received the B.E. degree in electronics and telecommunication engineering, the M.E. degree in electron devices, and the Ph.D. degree in microelectromechanical systems (MEMS)-based gas sensor and its integration with CMOS circuits from Jadavpur University, Kolkata, India, in 2002, 2004, and 2008, respectively.

He is currently an Assistant Professor with the Department of Electronics and Telecommunication Engineering, Indian Institute of Engineering Science and Technology at Shibpur, Shibpur, India. He has

authored about 100 research articles in reputed national and international journals and conferences. His current research interests include nanomaterial-based sensors, MEMS-based chemical sensors and its CMOS integration, and low-power VLSI design.

Dr. Bhattacharyya was a recipient of the Young Engineer's Award from the Institution of Engineers, India, in 2010, the CAREER Award for Young Teachers from the All India Council for Technical Education from 2011 to 2012, the Young Engineer Award from the Indian National Academy of Engineering in 2012, and the Young Scientist Medal from the Indian National Science Academy for his teaching and research contributions in 2012.

**Bijoy Kundu** received the B.E. degree from the Department of Electronics and Telecommunication Engineering, Indian Institute of Engineering Science and Technology at Shibpur, Shibpur, India, in 2013.

**Sovan Ghosh** received the B.E. degree from the Department of Electronics and Telecommunication Engineering, Indian Institute of Engineering Science and Technology at Shibpur, Shibpur, India, in 2013.

He is currently a Design Engineer with Cirel Systems Pvt. Ltd., Bangalore, India.

digital VLSI.

Vinay Kumar (M'14) received the B.Tech. degree in electronics and communication engineering from the North Eastern Regional Institute of Science and Technology, Nirjuli, India, in 2010, and the M.Tech. degree in microelectronics and VLSI design from the National Institute of Technology (NIT) Silchar, Silchar, India, in 2012.

He is currently an Assistant Professor with the Department of Electronics and Communication Engineering, NIT Meghalaya, Shillong, India. His current research interests include analog and

**Anup Dandapat** (M'10) received the Ph.D. degree in digital VLSI design from Jadavpur University, Kolkata, India, in 2008.

He is currently an Associate Professor with the Department of Electronics and Communication Engineering, National Institute of Technology Meghalaya, Shillong, India. He has authored over 50 national and international journal papers. His current research interests include low-power VLSI design and memory design.